7Host Interface Port

7 –

15

for the read cycle and the write cycle is as follows:

1. The host asserts ALE.

2. The host drives the address.

3. The host deasserts ALE.

4. The host stops driving the address.

5. The host asserts (H

RD or HWR) and HSEL.

6. The ADSP-21xx returns H

ACK (and, for a read cycle, the data).

7. For a write cycle, the host asserts the data.

8. The host deasserts (HRD or HWR) and HSEL.

9. For a write cycle, the host deasserts the data.

10. The ADSP-21xx deasserts H

ACK (and, for a read cycle, the data).

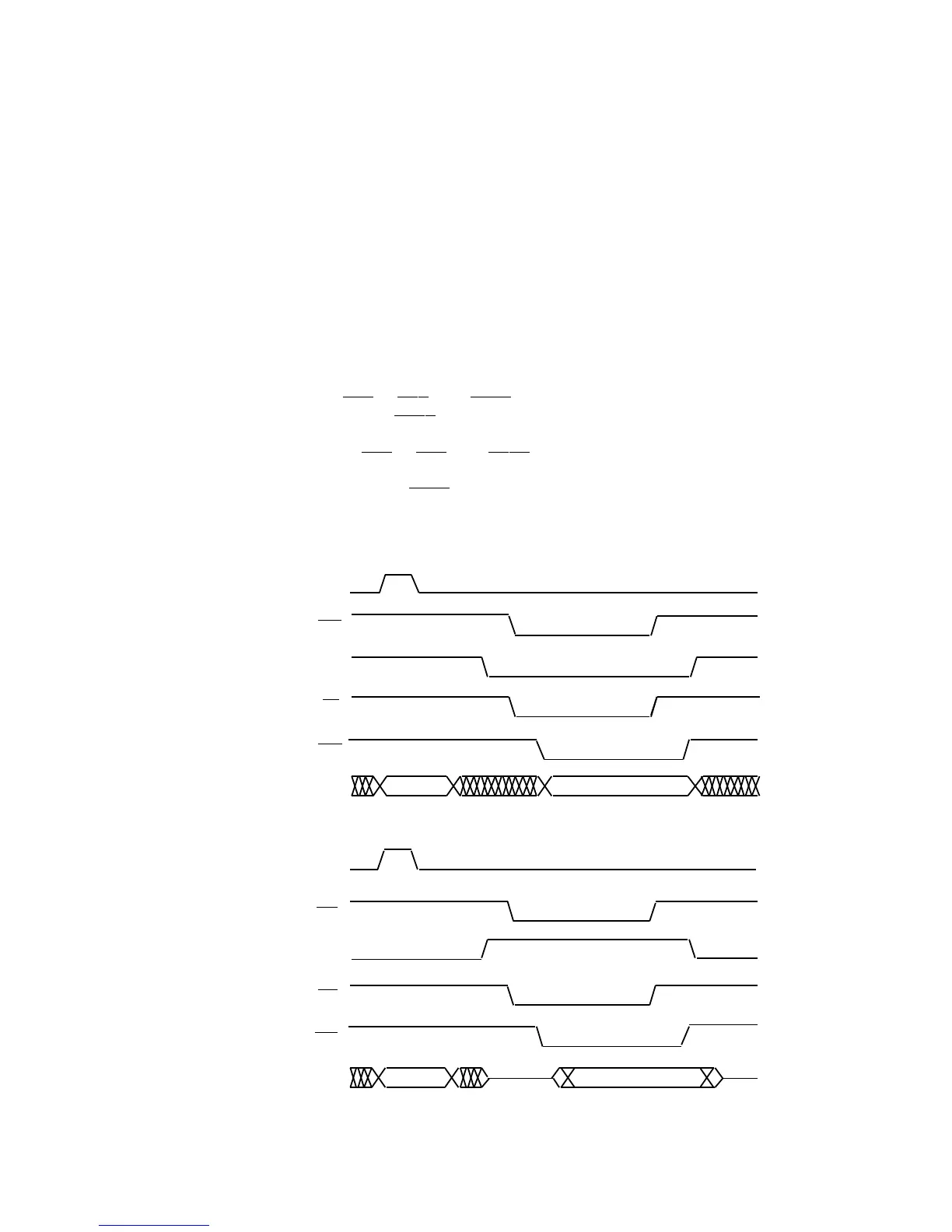

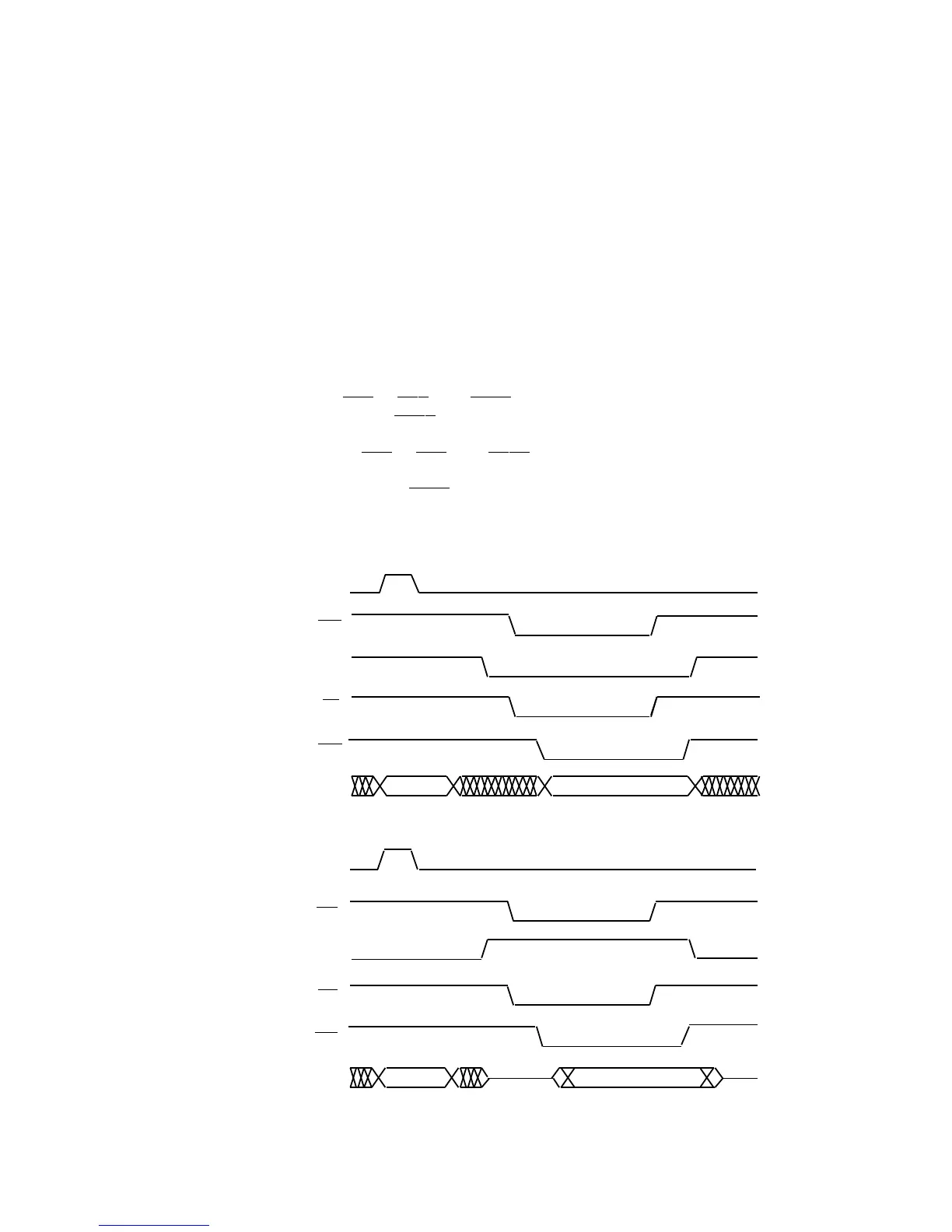

Figure 7.9 shows the HIP timing when HMD0=1 and HMD1=1. HMD0

selects a multiplexed read/write select with data strobe, and HMD1

selects multiplexed address and data buses. HD0-HD2 are used for the

address. The timing for the read cycle and the write cycle is as follows:

HSEL

HDS

HACK

HRW

ALE

DATA

HAD15–0

ADDRESS

HAD15–0 ADDRESS DATA

HSEL

HDS

HACK

HRW

ALE

Host Write Cycle

Host Read Cycle

Figure 7.9 HIP Timing: Multiplexed R/W Strobe, Multiplexed Buses

Loading...

Loading...