EControl/Status Registers

E – 7

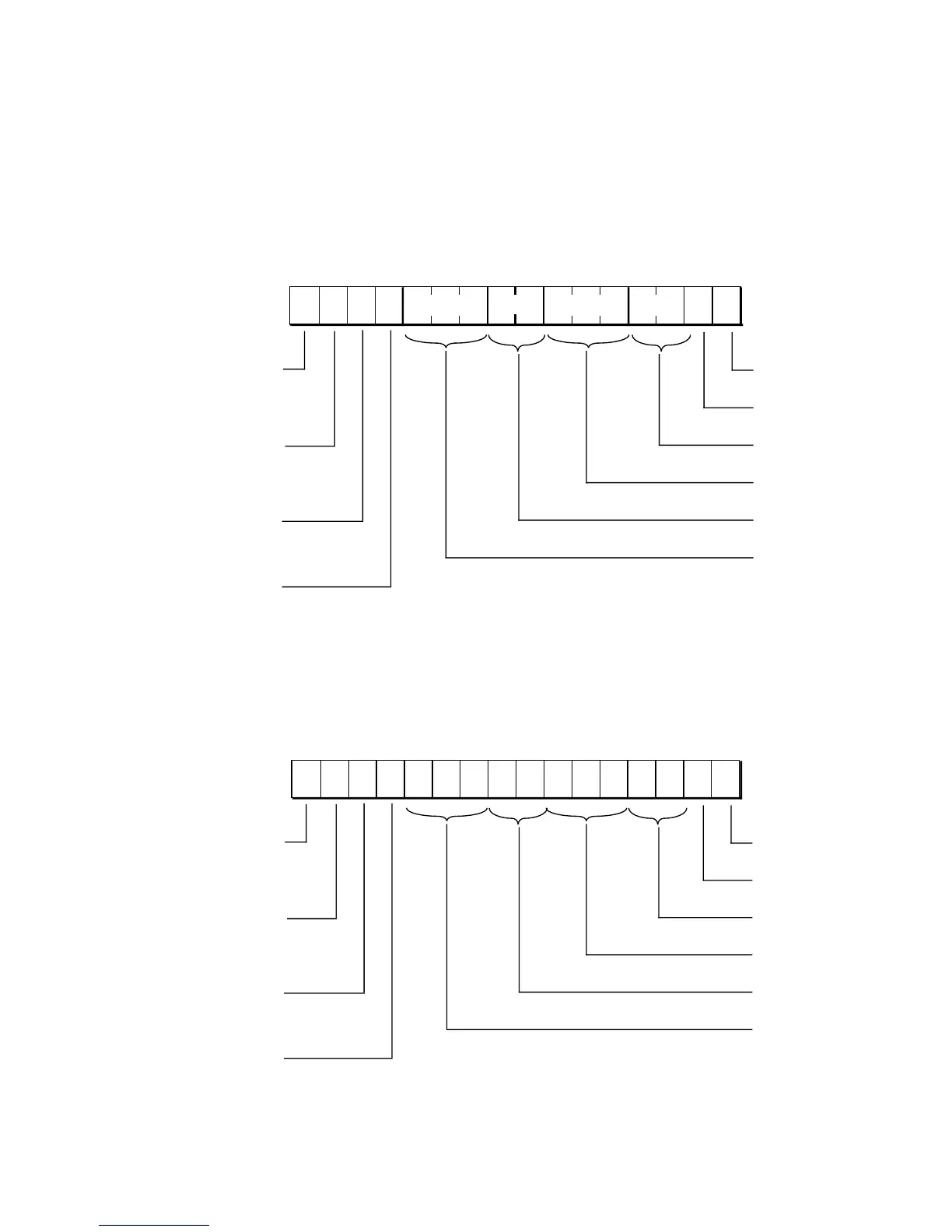

SPORT1 Autobuffer Control Register

1514131211109876 5432 10

TBUF

Transmit Autobuffer Enable

RBUF

Receive Autobuffer Enable

RMREG

Receive M register

RIREG

Receive I register

TMREG

Transmit M register

TIREG

Transmit I register

XTALDIS

XTAL Pin Disable During Powerdown

1=disabled, 0=enabled

(XTAL pin should be disabled when

no external crystal is connected)

XTALDELAY

Delay Startup From Powerdown 4096 Cycles

1=delay, 0=no delay

(use delay to allow internal phase locked

loop or external oscillator to stabilize)

PDFORCE

Powerdown Force

1=force processor to vector to

powerdown interrupt

PUCR

Powerup Context Reset

1=soft reset (clear context)

0=resume execution

0000 00

XTALDIS, XTALDELAY, PDFORCE, and PUCR are only on the

ADSP-2171, ADSP-2181, and ADSP-21msp58/59 processors.

DM(0x3FEF)

(Not on ADSP-21msp5x)

Default bit values at reset are shown; if no value is shown, the bit is undefined at reset.

Reserved bits are shown on a gray field—these bits should always be written with zeros.

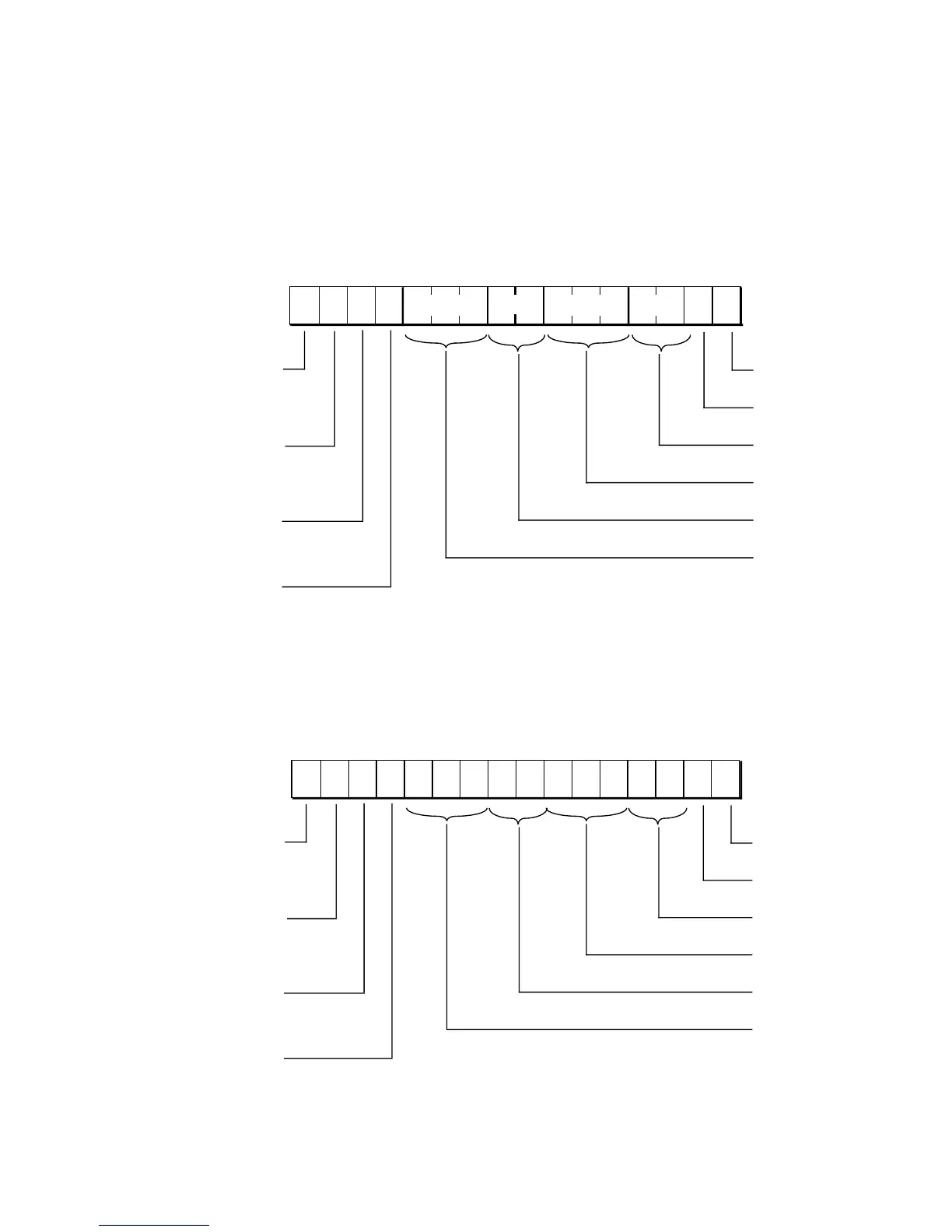

Memory-Mapped Registers

15141312111098 7654 32 10

ATBUF

DAC Transmit Autobuffer Enable

ARBUF

ADC Receive Autobuffer Enable

ARMREG

Receive M register

ARIREG

Receive I register

ATMREG

Transmit M register

ATIREG

Transmit I register

XTALDIS

XTAL Pin Disable During Powerdown

1=disabled, 0=enabled

(XTAL pin should be disabled when

no external crystal is connected)

XTALDELAY

Delay Startup From Powerdown 4096 Cycles

1=delay, 0=no delay

PDFORCE

Powerdown Force

1=force processor to vector to

powerdown interrupt

PUCR

Powerup Context Reset

1=soft reset, 0=resume execution

000000

(ADSP-21msp5x only)

Analog Autobuffer Control Register

DM(0x3FEF)

Loading...

Loading...