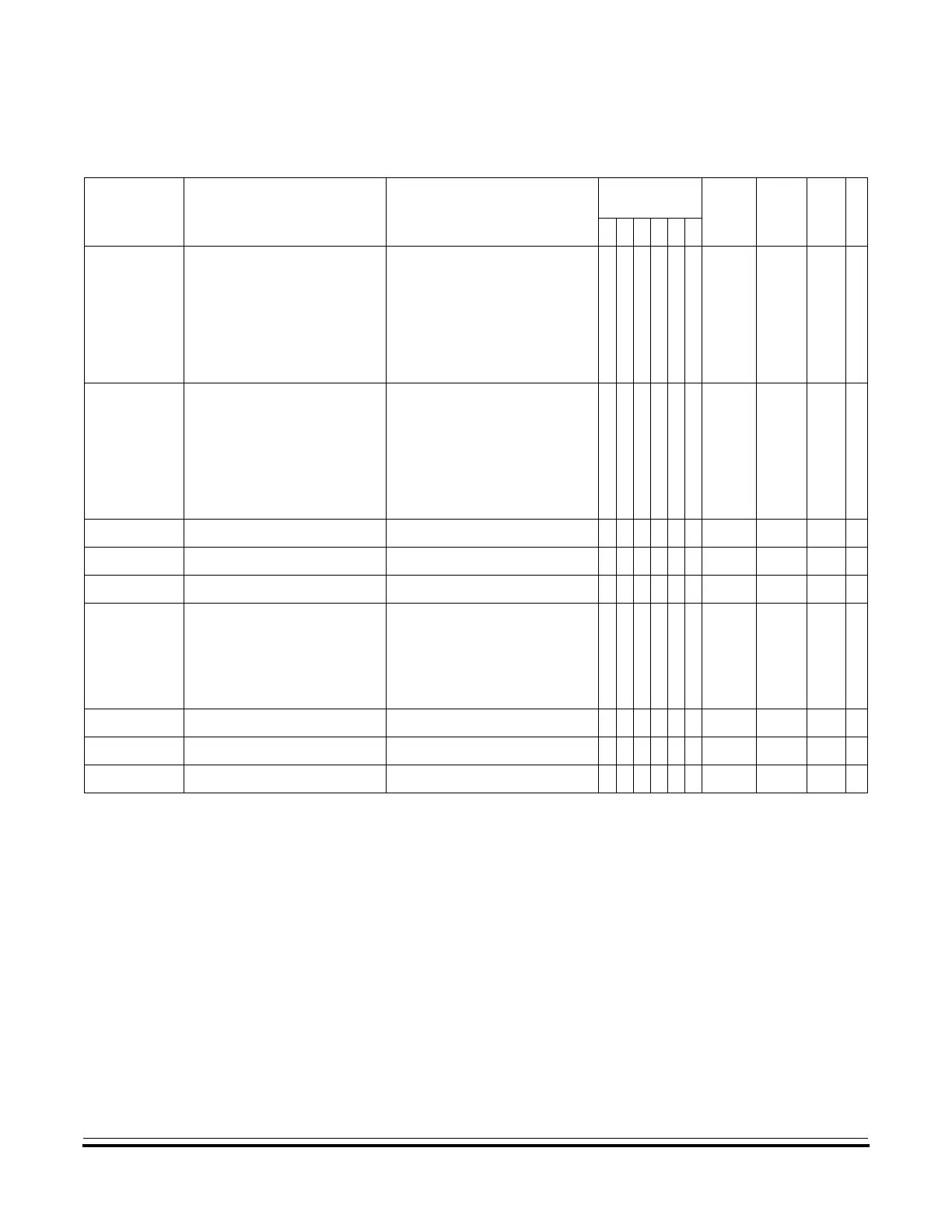

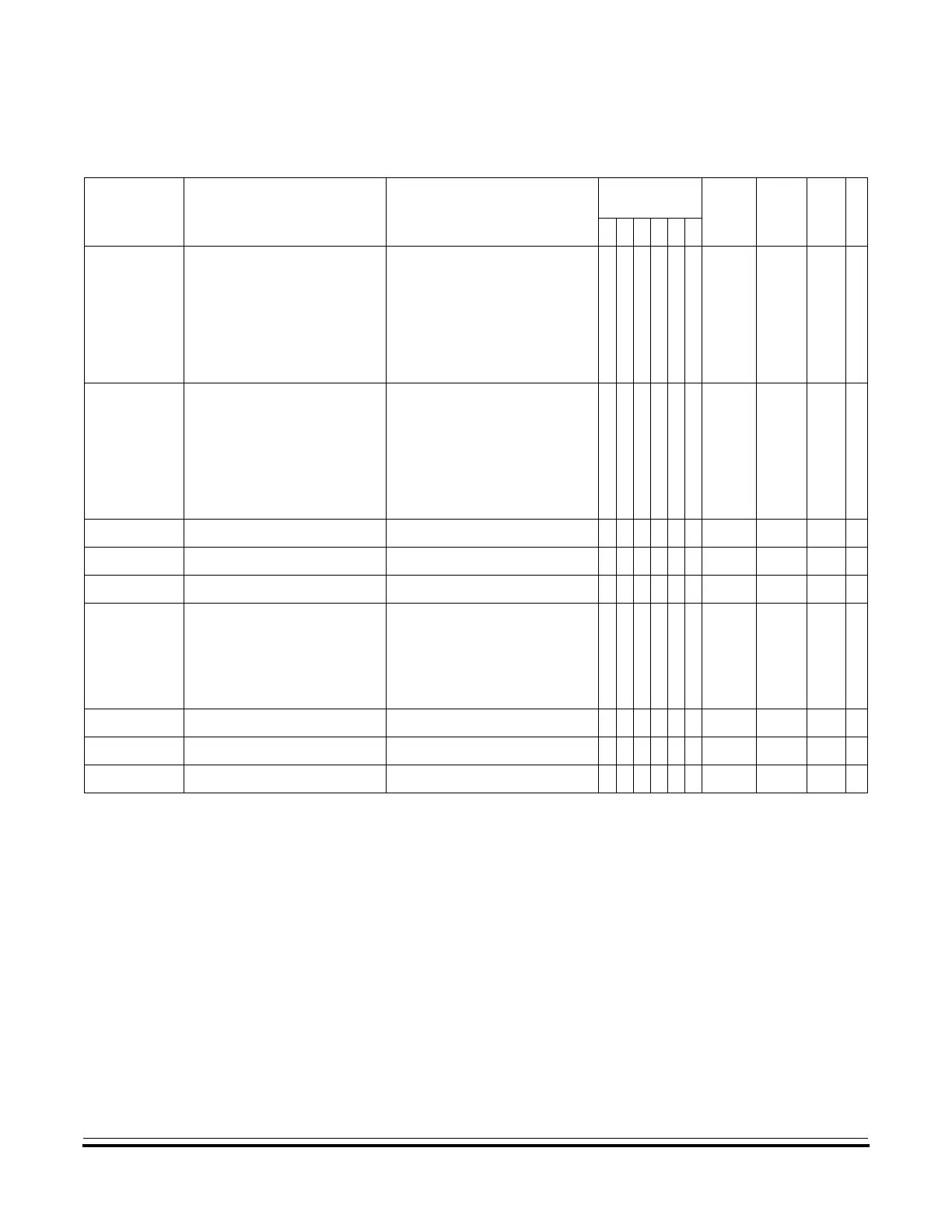

Central Processor Unit (CPU)

Opcode Map

MC68HC908AB32 — Rev. 1.0 Technical Data

MOTOROLA Central Processor Unit (CPU) 105

SUB #

opr

SUB

opr

SUB

opr

SUB

opr

,X

SUB

opr

,X

SUB ,X

SUB

opr

,SP

SUB

opr

,SP

Subtract A ← (A) – (M) ↕ ––↕↕↕

IMM

DIR

EXT

IX2

IX1

IX

SP1

SP2

A0

B0

C0

D0

E0

F0

9EE0

9ED0

ii

dd

hh ll

ee ff

ff

ff

ee ff

2

3

4

4

3

2

4

5

SWI Software Interrupt

PC ← (PC) + 1; Push (PCL)

SP ← (SP) – 1; Push (PCH)

SP ← (SP) – 1; Push (X)

SP ← (SP) – 1; Push (A)

SP ← (SP) – 1; Push (CCR)

SP ← (SP) – 1; I ← 1

PCH ← Interrupt Vector High Byte

PCL ← Interrupt Vector Low Byte

––1–––INH 83 9

TAP Transfer A to CCR CCR ← (A) ↕↕↕↕↕↕INH 84 2

TAX Transfer A to X X ← (A) ––––––INH 97 1

TPA Transfer CCR to A A ← (CCR) ––––––INH 85 1

TST

opr

TSTA

TSTX

TST

opr

,X

TST ,X

TST

opr

,SP

Test for Negative or Zero (A) – $00 or (X) – $00 or (M) – $00 0 – – ↕↕–

DIR

INH

INH

IX1

IX

SP1

3D

4D

5D

6D

7D

9E6D

dd

ff

ff

3

1

1

3

2

4

TSX Transfer SP to H:X H:X ← (SP) + 1 ––––––INH 95 2

TXA Transfer X to A A ← (X) ––––––INH 9F 1

TXS Transfer H:X to SP (SP) ← (H:X) – 1 ––––––INH 94 2

Table 7-1. Instruction Set Summary (Continued)

Source

Form

Operation Description

Effect on

CCR

Address

Mode

Opcode

Operand

Cycles

VHINZC

Loading...

Loading...