S3F84B8_UM_REV 1.00 6 INSTRUCTION SET

6-61

6.3.48 OR — LOGICAL OR

OR dst,src

Operation: dst dst OR src

The source operand is logically ORed with the destination operand, and the result is stored in

destination. The contents of source remain unaffected. The OR operation results in a “1” being

stored whenever either of the corresponding bits in two operands is a “1”; otherwise a “0” is

stored.

Flags: C: Unaffected.

Z: Set if the result is “0”; cleared otherwise.

S: Set if the result bit 7 is set; cleared otherwise.

V: Always cleared to “0”.

D: Unaffected.

H: Unaffected.

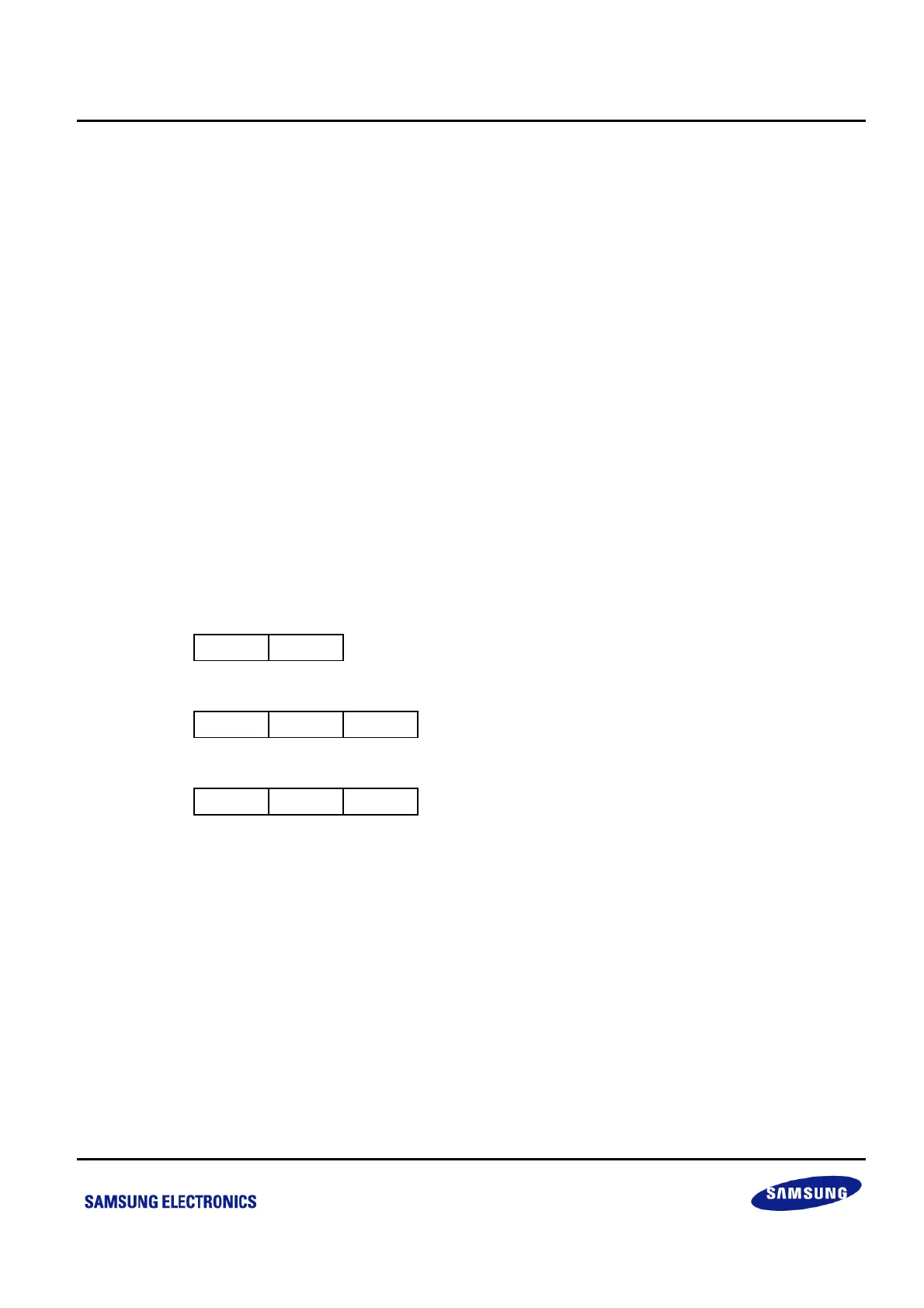

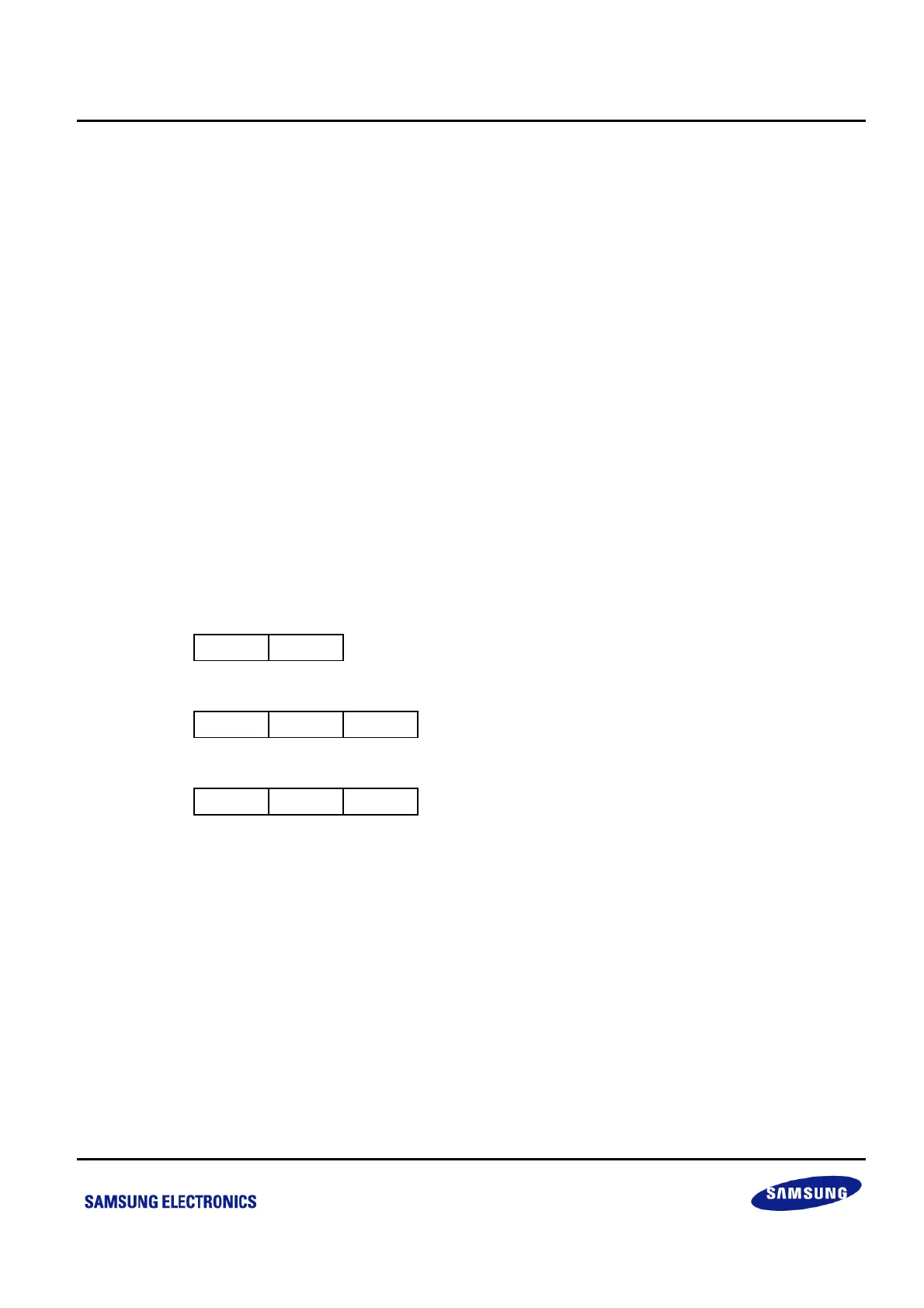

Format:

Bytes Cycles Opcode

(Hex)

Addr Mode

dst src

opc dst | src 2 4 42 r r

6 43 r lr

opc src dst 3 6 44 R R

6 45 R IR

opc dst src 3 6 46 R IM

Examples: Given R0 = 15H, R1 = 2AH, R2 = 01H, register 00H = 08H, register 01H = 37H, and register 08H

= 8AH:

OR R0,R1 R0 = 3FH, R1 = 2AH

OR R0,@R2 R0 = 37H, R2 = 01H, register 01H = 37H

OR 00H,01H Register 00H = 3FH, register 01H = 37H

OR 01H,@00H Register 00H = 08H, register 01H = 0BFH

OR 00H,#02H Register 00H = 0AH

In the first example, if working register R0 contains the value 15H and register R1 contains the

value 2AH, the statement “OR R0,R1” logical-ORs the R0 and R1 register contents and stores

the result (3FH) in destination register R0.

Other examples show the use of logical OR instruction with the various addressing modes and

formats.

Loading...

Loading...