S3F84B8_UM_REV 1.00 4 CONTROL REGISTERS

4-12

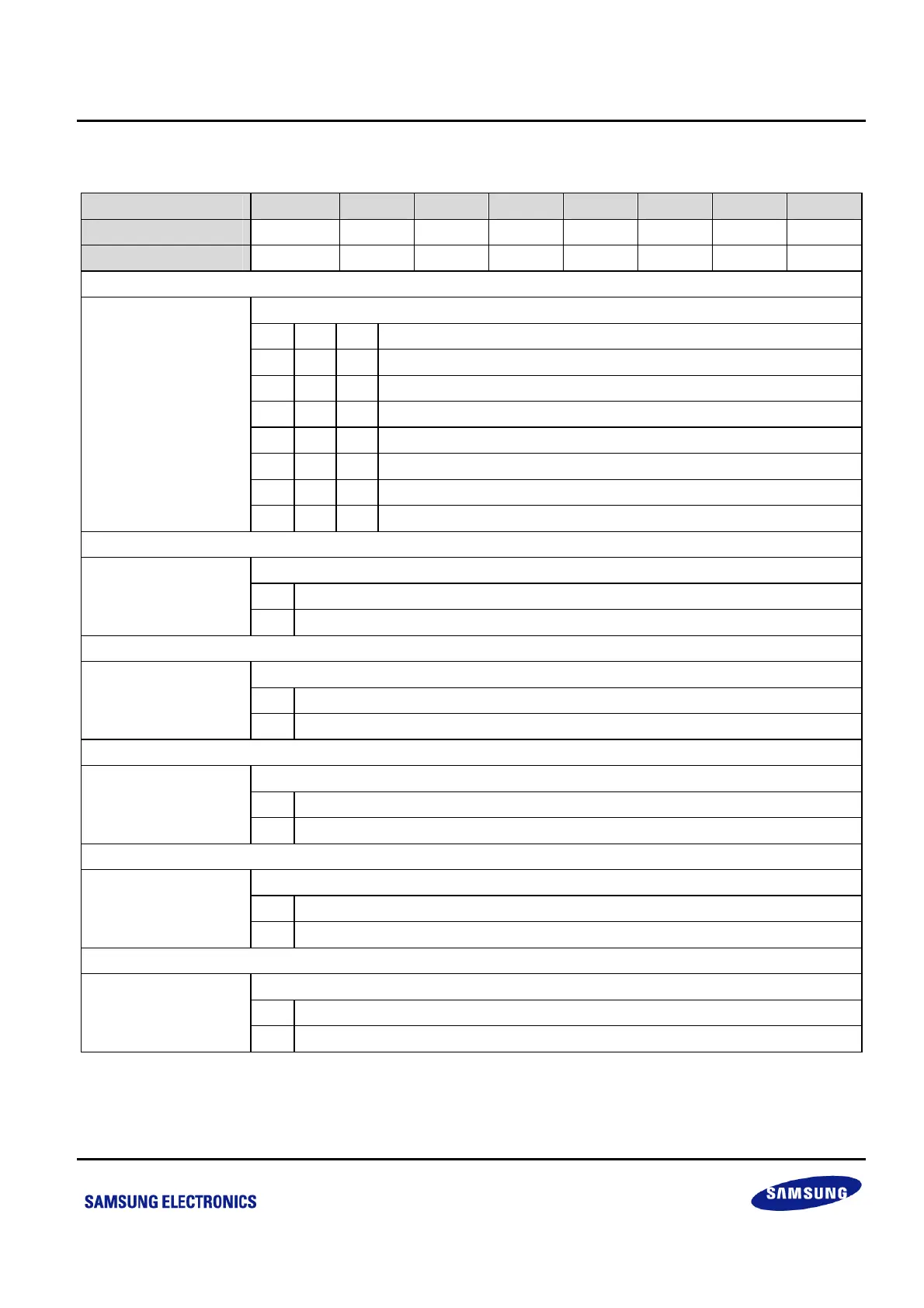

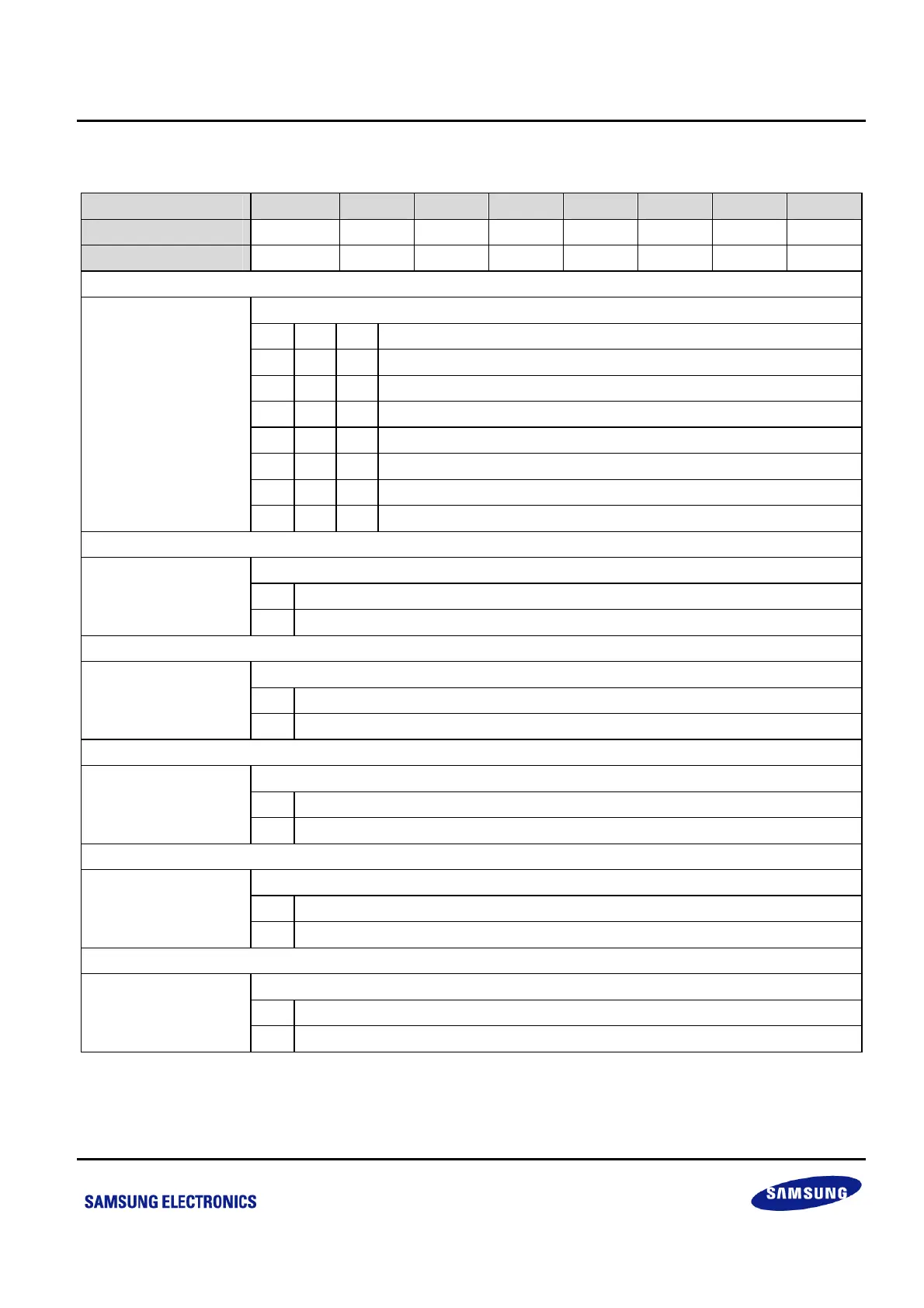

4.1.9 CMP3CON — COMPARATOR1 CONTROL REGISTER: EDH, BANK0

Bit Identifier .7 .6 .5 .4 .3 .2 .1 .0

RESET Value

0 0 0 0 0 0 1 0

Read/Write

R/W R/W R/W R/W R/W R/W R R/W

Comparator3 Reference Level Selection Bit

0 0 0 0.45VDD

0 0 1 0.50VDD

0 1 0 0.55VDD

0 1 1 0.60VDD

1 0 0 0.65VDD

1 0 1 0.70VDD

1 1 0 0.75VDD

.7–.5

1 1 1 0.80VDD

Comparator3 Output Polarity Select Bit

0 Does not invert CMP3 output.

.4

1 Inverts CMP3 output.

Comparator3 Enable Bit

0 Disables comparator3.

.3

1 Enables comparator3.

Comparator3 Interrupt Enable Bit

0 Disables CMP3 interrupt.

.2

1 Enables CMP3 interrupt.

Comparator3 Status Bit

0 CMP3_N > CMP3_P

.1

1 CMP3_N < CMP3_P

Comparator3 Pending Bit

0 No interrupt is pending (clears pending bit when write).

.0

1 CMP3 interrupt is pending.

NOTE:

1. Polarity selection bit (CMP3CON.4) will not affect the interrupt generation logic.

2. Refer to “Programming Tip” in Chapter 14 for proper configuration sequence.

Loading...

Loading...