S3F84B8_UM_REV 1.00 4 CONTROL REGISTERS

4-20

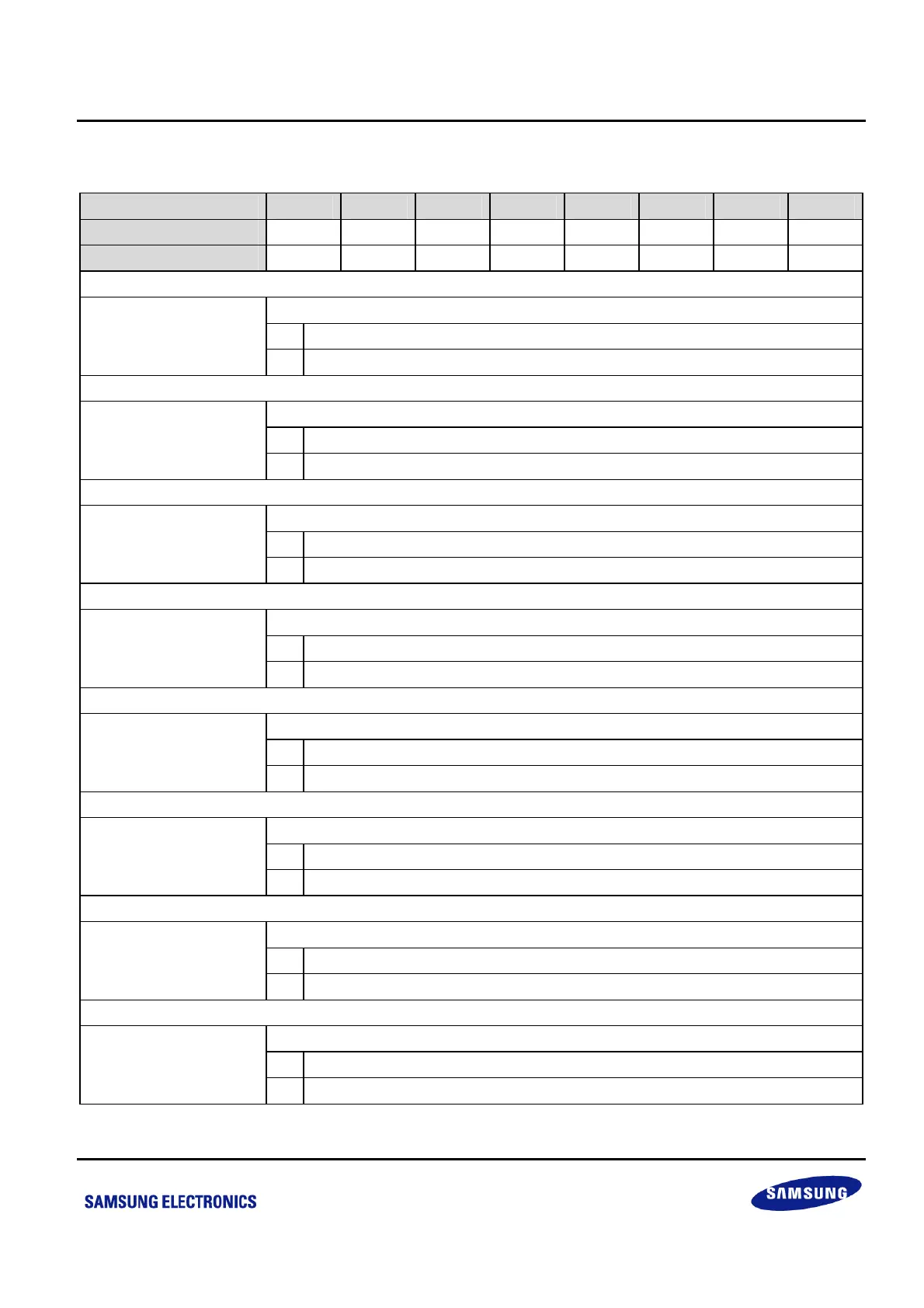

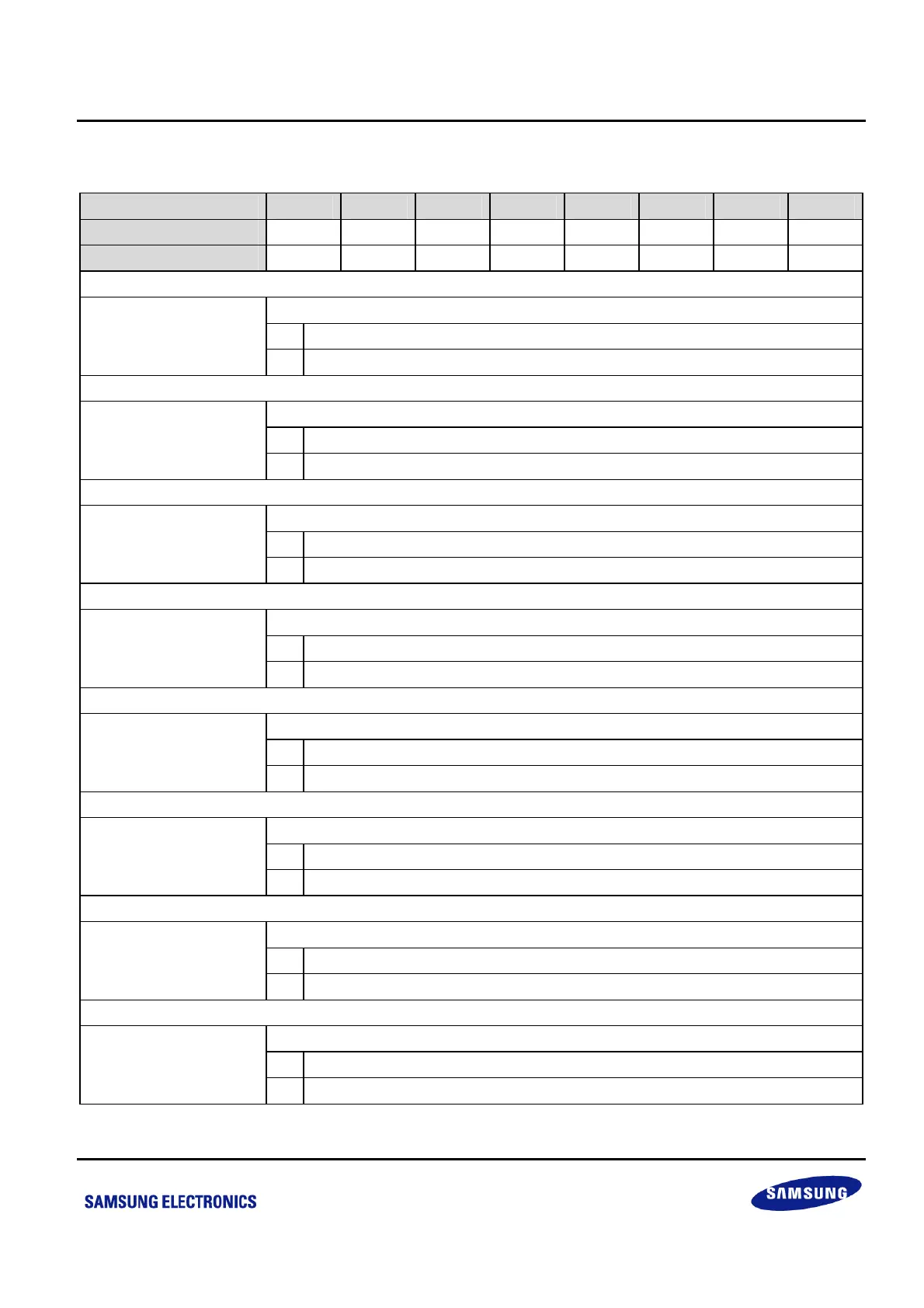

4.1.20 IRQ — INTERRUPT REQUEST REGISTER: DCH, BANK0

Bit Identifier .7 .6 .5 .4 .3 .2 .1 .0

Reset Value

0 0 0 0 0 0 0 0

Read/Write

R R R R R R R R

Level 7 (IRQ7) Request Pending Bit

0 Not pending

.7

1 Pending

Level 6 (IRQ6) Request Pending Bit

0 Not pending

.6

1 Pending

Level 5 (IRQ5) Request Pending Bit

0 Not pending

.5

1 Pending

Level 4 (IRQ4) Request Pending Bit

0 Not pending

.4

1 Pending

Level 3 (IRQ3) Request Pending Bit

0 Not pending

.3

1 Pending

Level 2 (IRQ2) Request Pending Bit

0 Not pending

.2

1 Pending

Level 1 (IRQ1) Request Pending Bit

0 Not pending

.1

1 Pending

Level 0 (IRQ0) Request Pending Bit

0 Not pending

.0

1 Pending

Loading...

Loading...