S3F84B8_UM_REV 1.00 4 CONTROL REGISTERS

4-13

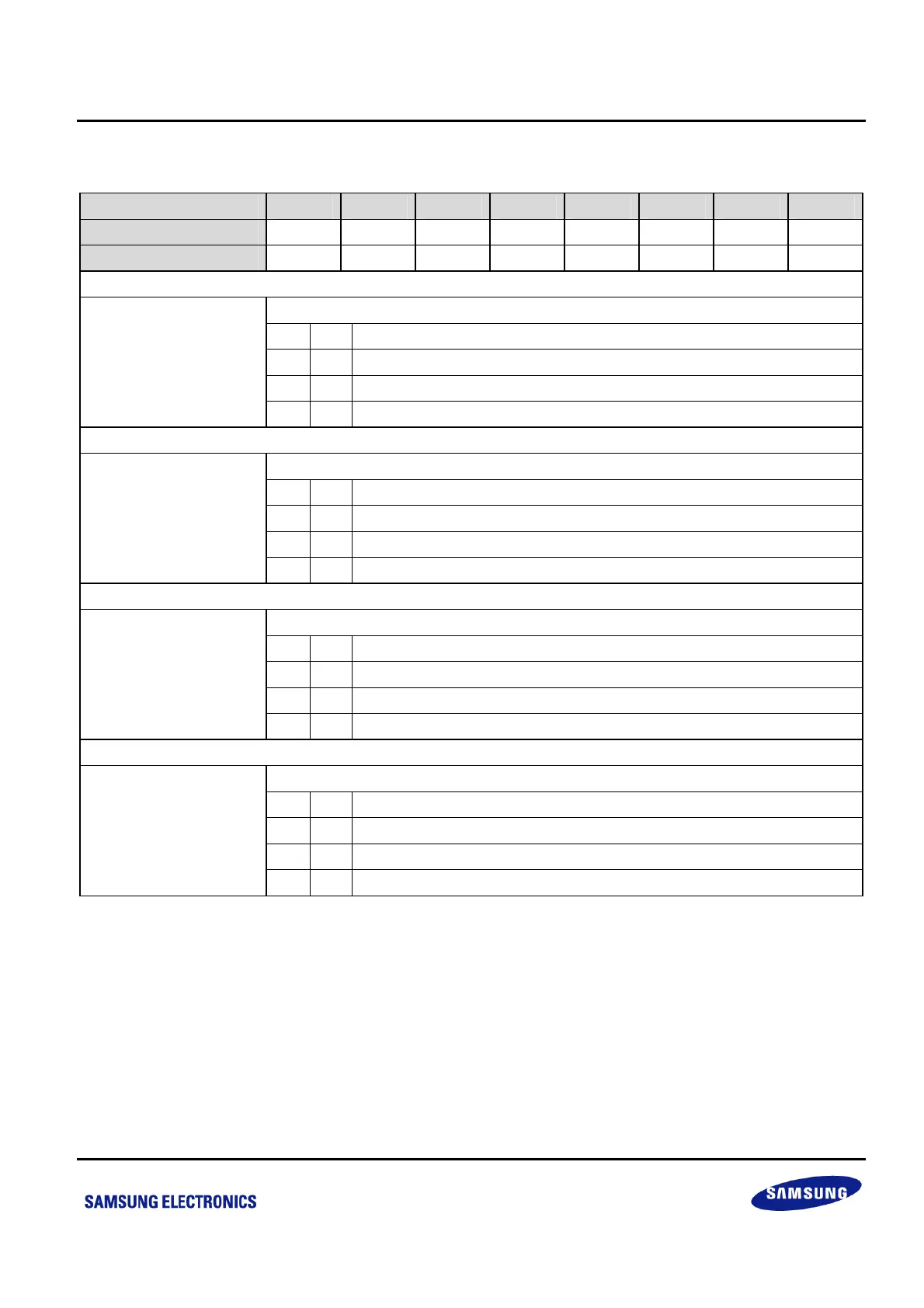

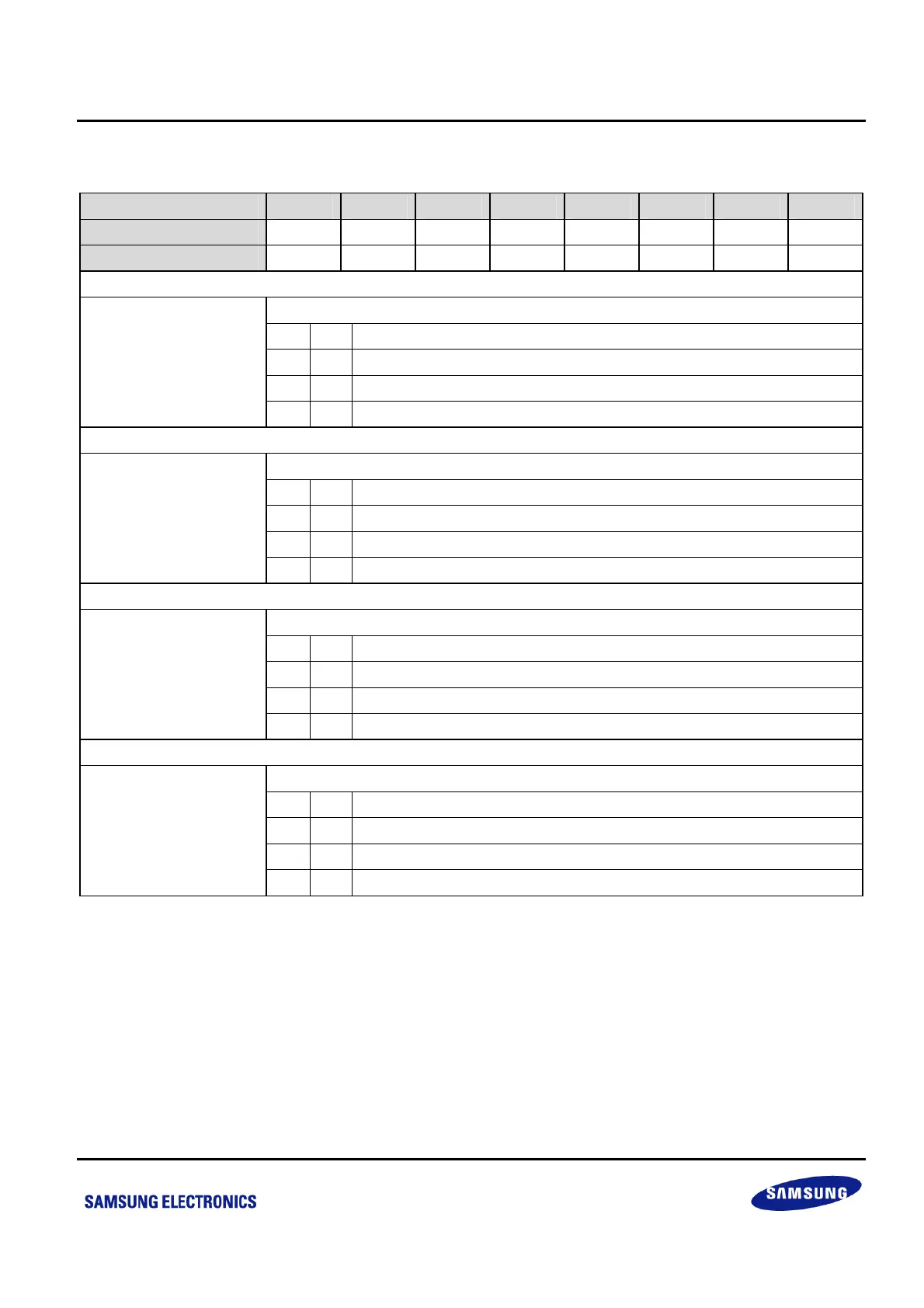

4.1.10 CMPINT — COMPARATOR INTERRUPT MODE CONTROL REGISTER: EEH, BANK0

Bit Identifier .7 .6 .5 .4 .3 .2 .1 .0

RESET Value

1 1 1 1 1 1 1 1

Read/Write

R/W R/W R/W R/W R/W R/W R/W R/W

CMP3 Interrupt Mode Selection Bit

0 0 Invalid setting

0 1 Falling edge interrupt

1 0 Rising edge interrupt

.7–.6

1 1 Falling and rising edge interrupt

CMP2 Interrupt mode selection bit

0 0 Invalid setting

0 1 Falling edge interrupt

1 0 Rising edge interrupt

.5–.4

1 1 Falling and rising edge interrupt

CMP1 Interrupt mode selection bit

0 0 Invalid setting

0 1 Falling edge interrupt

1 0 Rising edge interrupt

.3–.2

1 1 Falling and rising edge interrupt

CMP0 Interrupt mode selection bit

0 0 Invalid setting

0 1 Falling edge interrupt

1 0 Rising edge interrupt

.1–.0

1 1 Falling and rising edge interrupt

NOTE: When CMP0/1/2/3 interrupt is used, the CMPINT register must be set to appropriate value before enabling

CMP0/1/2/3.

Loading...

Loading...