S3F84B8_UM_REV 1.00 4 CONTROL REGISTERS

4-29

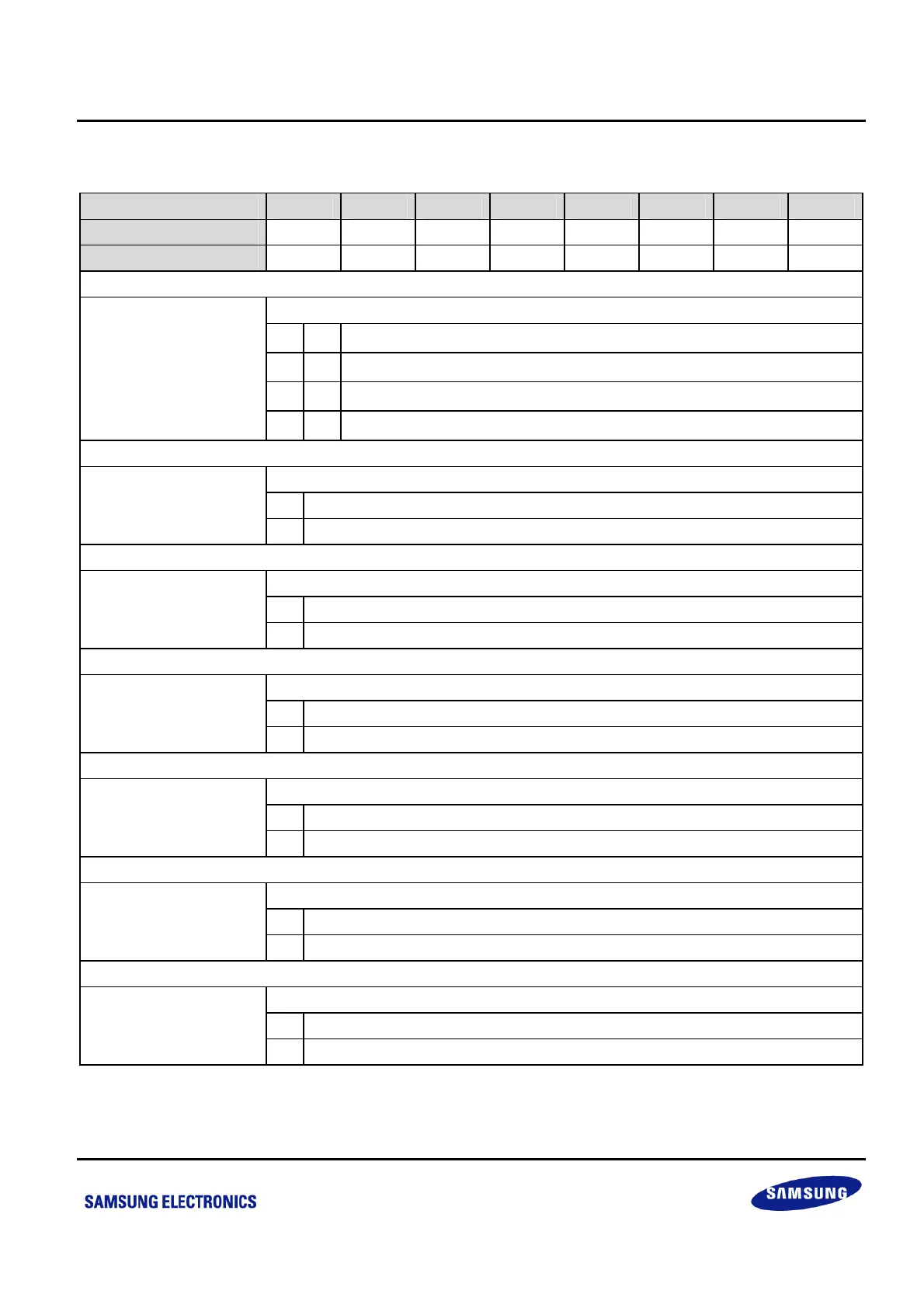

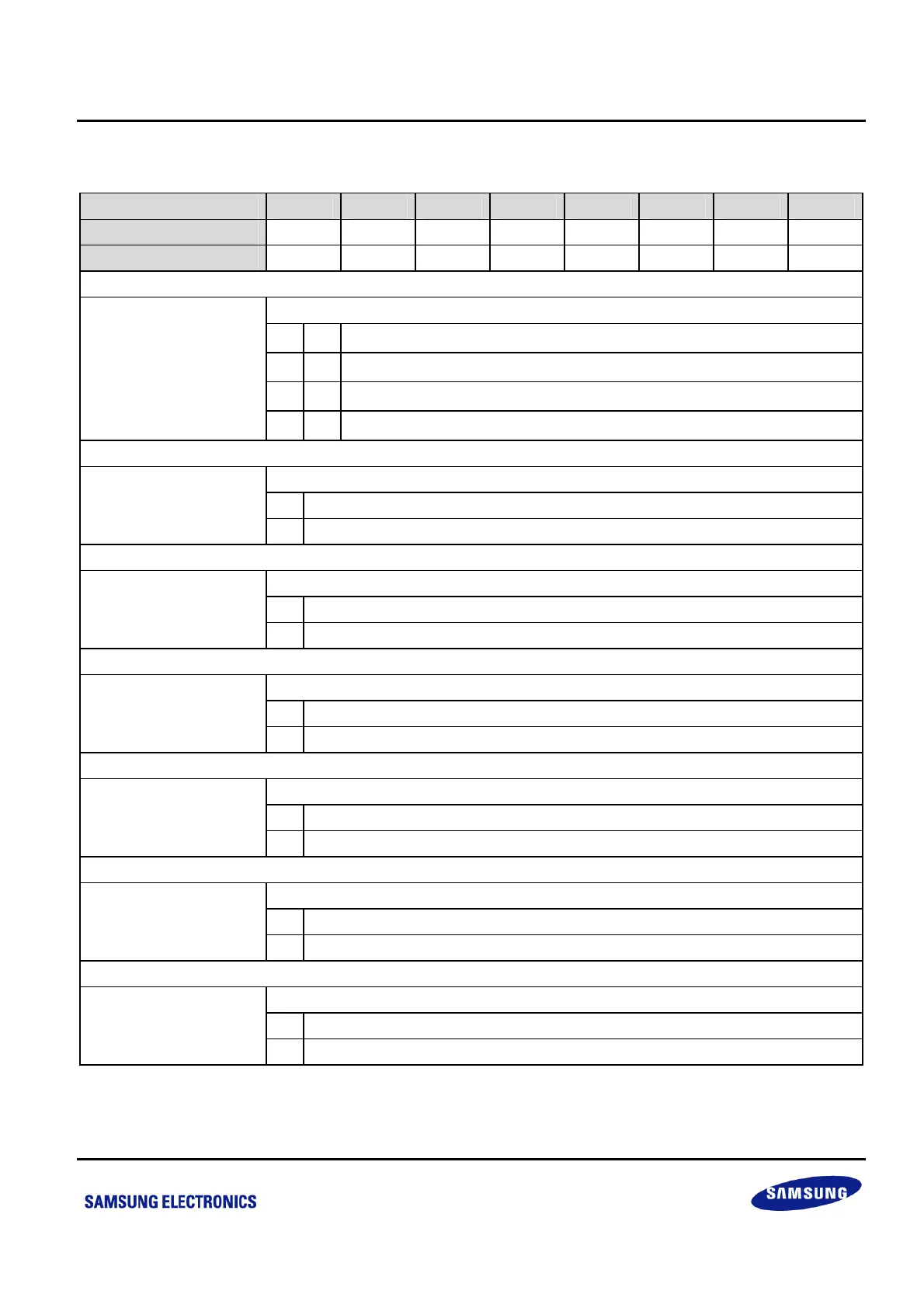

4.1.29 PWMCON — PWM CONTROL REGISTER: EFH, BANK0

Bit Identifier .7 .6 .5 .4 .3 .2 .1 .0

RESET Value

0 0 0 0 0 0 0 0

Read/Write

R/W R/W R/W R/W R/W R/W R/W R/W

PWM Input Clock Select Bits

0 0

f

OSC

/64

0 1

f

OSC

/8

1 0

f

OSC

/2

.7–.6

1 1

f

OSC

/1

PWM Output Polarity Select Bit

0 Non-inverting output

.5

1 Inverting output

PWM Counter Clear Bit

0 No effect.

.4

1 Clears the PWM counter (when write).

PWM Counter Enable Bit

0 Stops counter.

.3

1 Starts counter (unlock operation).

Anti-Mis-Trigger Enable Bit

0 Disables anti-mis-trigger function.

.2

1 Enables anti-mis-trigger function.

PWM Overflow Interrupt Enable Bit

0 Disables interrupt.

.1

1 Enables interrupt.

PWM Overflow Interrupt Pending Bit

0 No interrupt is pending; clears pending bit (when write).

.0

1 Interrupt is pending; no effect (when write).

NOTE: To use anti-mis-trigger function, you must enable the linkage of CMP0 and PWM by setting PWMCCON.0 = 1.

Loading...

Loading...