S3F84B8_UM_REV 1.00 14 COMPARATOR

14-6

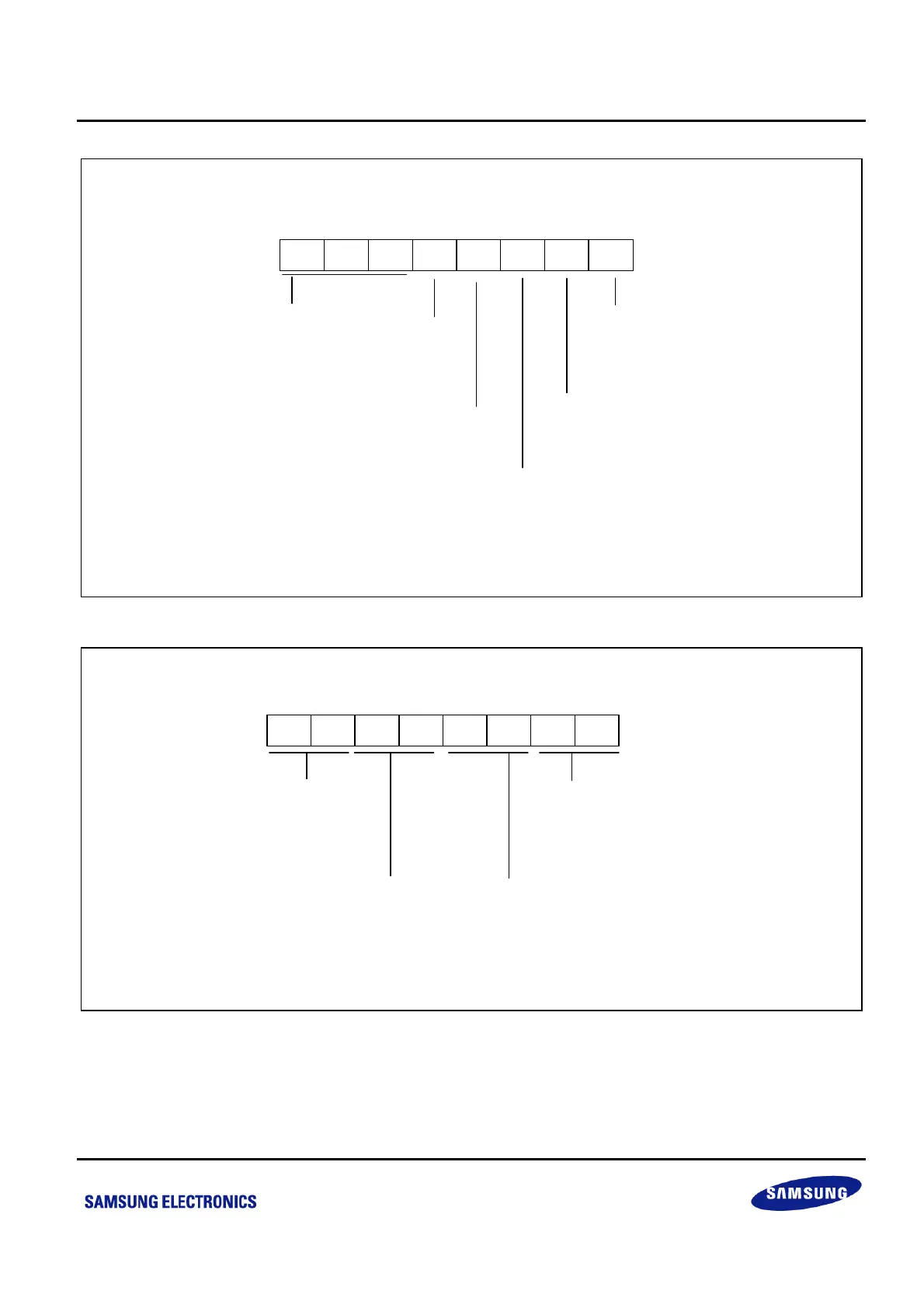

CMP3 Control Register (CMP3CON)

EDH, Set1, Bank0, Reset = 02H, R/W

.7 .6 .5 .4 .3 .2 .1 .0MSB LSB

CMP3 status bit

0=CMP3_N>CMP3_P

1=CMP3_N<CMP3_P

CMP 3 interrupt pending bit:

0 = No interrupt pending

(Clear pending bit when write)

1

= Interrupt is pending

CMP3 Interrupt enable bit

0 = Disable interrupt

1 = Enable interrupt

CMP 3 output polarity select bit

0 = CMP3 output is not inverted

1 = CMP3 output is inverted

CMP3 enable bit

0 = Disable comparator

1 = Enable comparator

CMP 3 reference level select bit

000 = 0.45VDD

001 = 0.50VDD

010 = 0.55VDD

011 = 0.60VDD

100 = 0.65VDD

101 = 0.70VDD

110 = 0.75VDD

111 = 0.80VDD

NOTE: Please refer to the programming tip for proper configuration sequence.

Figure 14-6 CMP3 Control Register (CMP3CON)

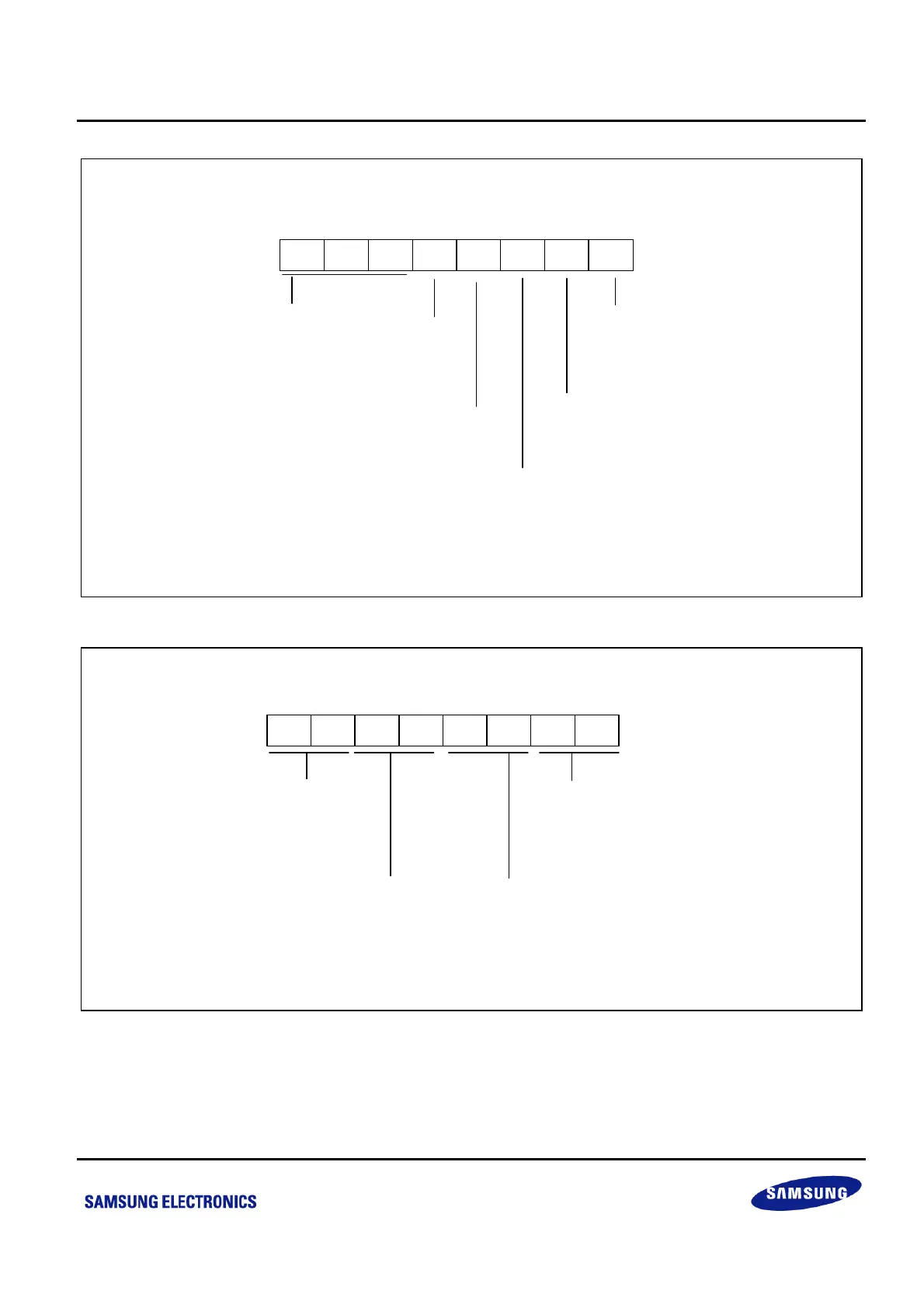

CMP Interrupt Mode Control Register (CMPINT)

EDH, Set1, Bank0, Reset = FFH, R/W

.7 .6 .5 .4 .3 .2 .1 .0MSB LSB

CMP3 interrupt mode selection

0 0 = invalid setting

01 = Falling edge

10 = Rising edge

11 = Falling and rising edge

CMP2 interrupt mode selection

0 0 = invalid setting

01 = Falling edge

10 = Rising edge

11 = Falling and rising edge

CMP0 interrupt mode selection

0 0 = invalid setting

01 = Falling edge

10 = Rising edge

11 = Falling and rising edge

CMP1 interrupt mode selection

0 0 = invalid setting

01 = Falling edge

10 = Rising edge

11 = Falling and rising edge

Figure 14-7 CMP Interrupt Mode Control Register (CMPINT)

Loading...

Loading...