S3F84B8_UM_REV 1.00 4 CONTROL REGISTERS

4-30

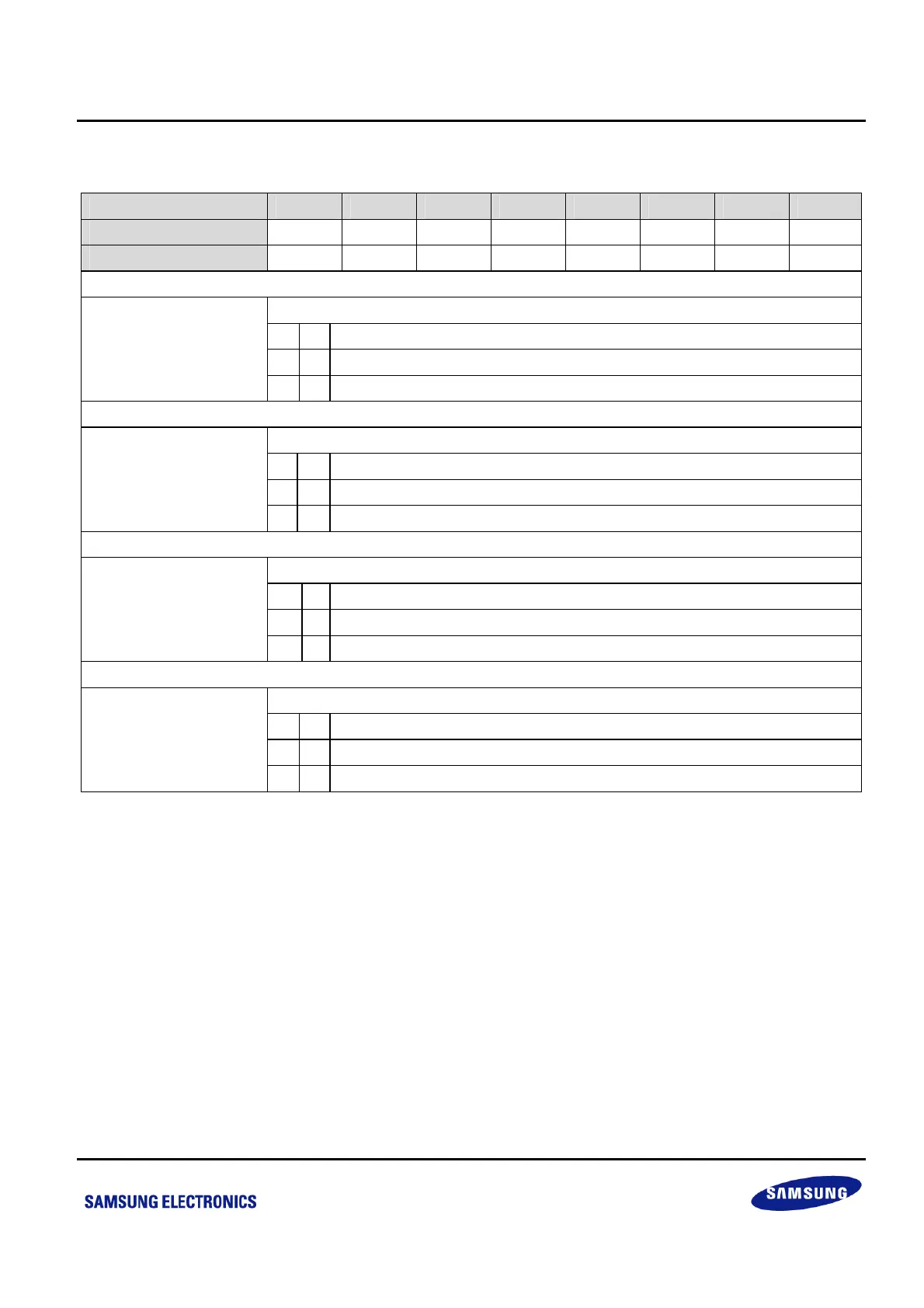

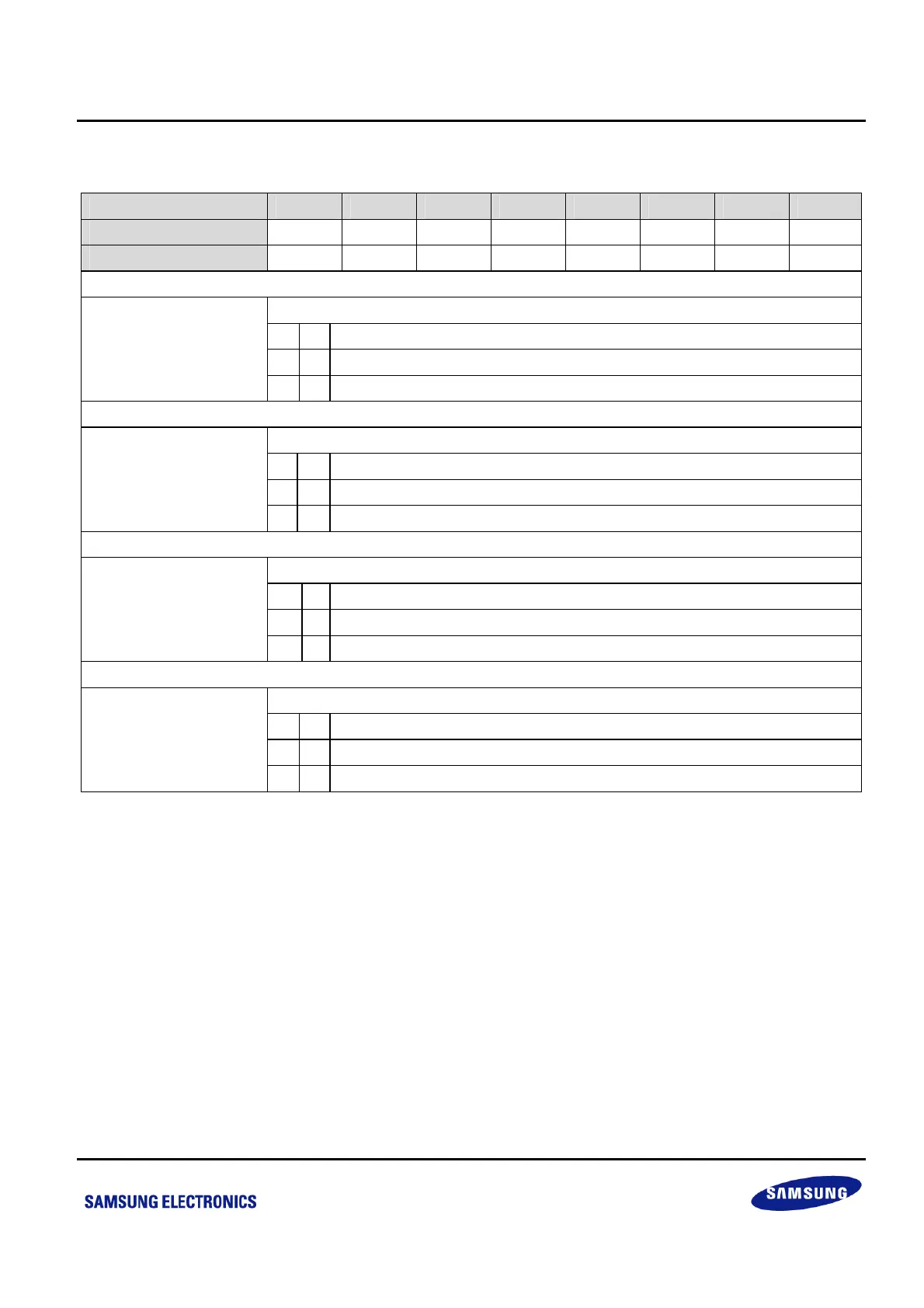

4.1.30 PWMCCON — PWM CMP CONTROL REGISTER: F0H, BANK0

Bit Identifier .7 .6 .5 .4 .3 .2 .1 .0

RESET Value

0 0 0 0 0 0 0 0

Read/Write

R/W R/W R/W R/W R/W R/W R/W R/W

CMP3 PWM Linkage Mode Selection Bits

X 0 Disables linkage.

0 1 Soft Lock

.7–.6

1 1 Hard lock

CMP2 PWM Linkage Mode Selection Bit

X 0 Disables linkage.

0 1 Soft Lock

.5–.4

1 1 Hard lock

CMP1 PWM Lock Mode Selection Bit

X 0 Disables linkage.

0 1 Soft Lock

.3–.2

1 1 Hard lock

CMP0 PWM Trigger Mode Selection Bit

X 0 Disables linkage.

0 1 Normal trigger

.1–.0

1 1 Delay trigger

NOTE: When CMP-PWM linkage is used, PWMCCON must be set to appropriate value before enabling PWM.

Loading...

Loading...