S3F84B8_UM_REV 1.00 4 CONTROL REGISTERS

4-34

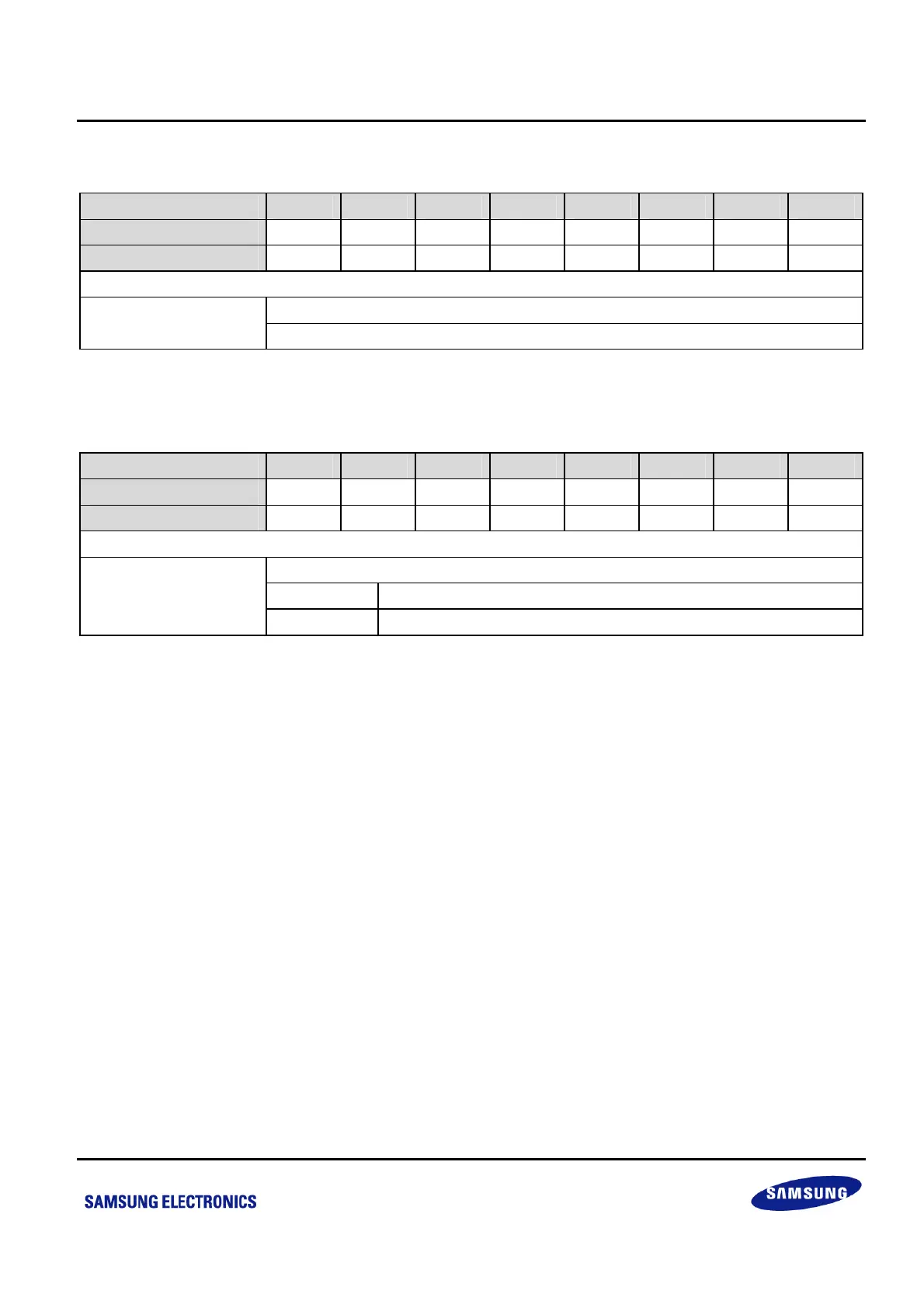

4.1.36 SPL — STACK POINTER: D9H, BANK0

Bit Identifier .7 .6 .5 .4 .3 .2 .1 .0

Reset Value

x x x x x x x x

Read/Write

R/W R/W R/W R/W R/W R/W R/W R/W

Stack Pointer Address (Low Byte) .7–.0

The SP value is undefined following a reset.

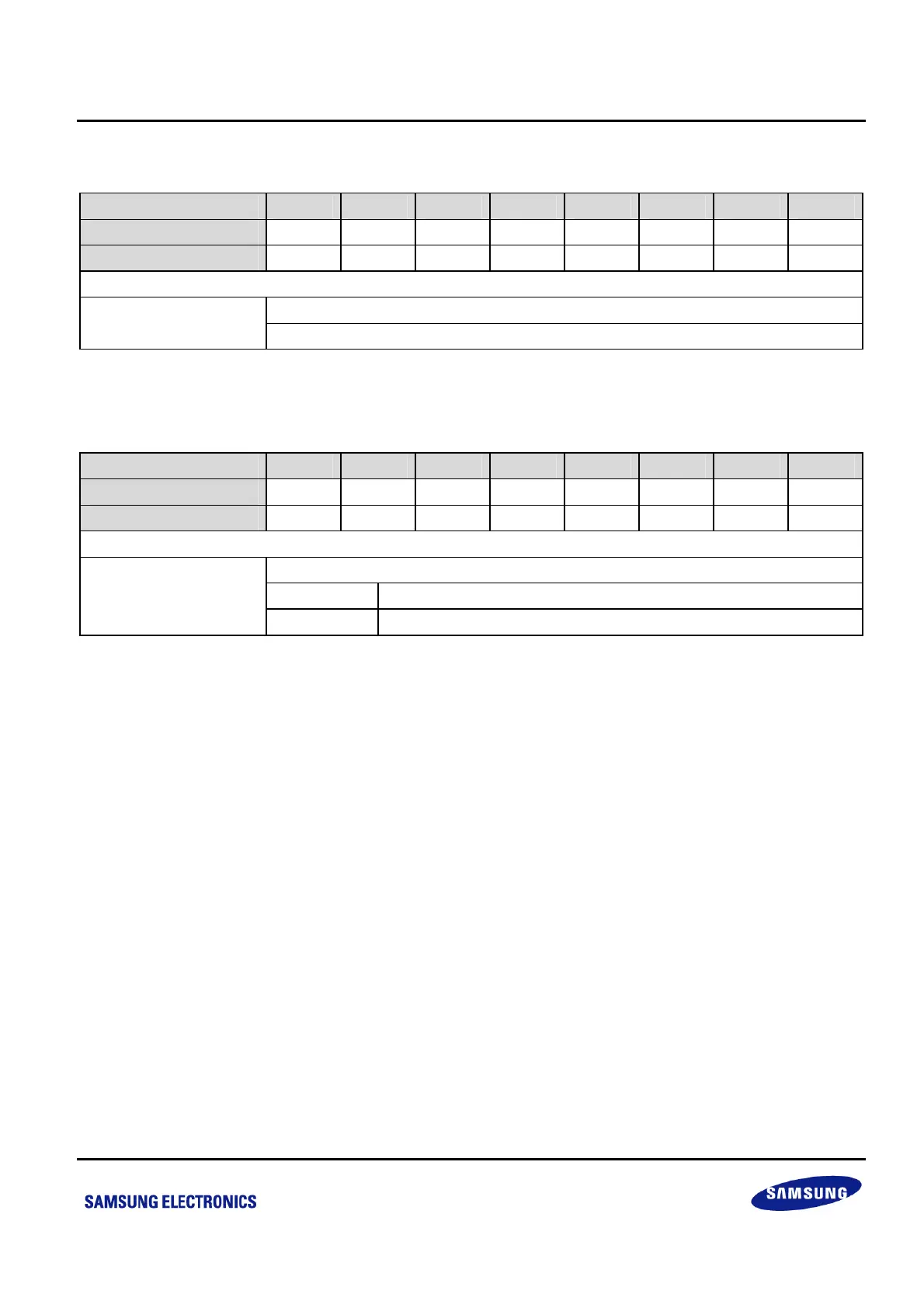

4.1.37 STOPCON — STOP MODE CONTROL REGISTER: F4H, BANK1

Bit Identifier .7 .6 .5 .4 .3 .2 .1 .0

RESET Value

0 0 0 0 0 0 0 0

Read/Write

R/W R/W R/W R/W R/W R/W R/W R/W

Watchdog Timer Function Enable Bit

10100101 Enables STOP instruction.

.7–.0

Other value Disables STOP instruction.

NOTE:

1. Before executing the STOP instruction, set this STPCON register to “10100101b”.

2. When STOPCON register does not have #0A5H value and you use STOP instruction, PC is changed to reset address.

Loading...

Loading...