S3F84B8_UM_REV 1.00 12 TIMER 0

12-3

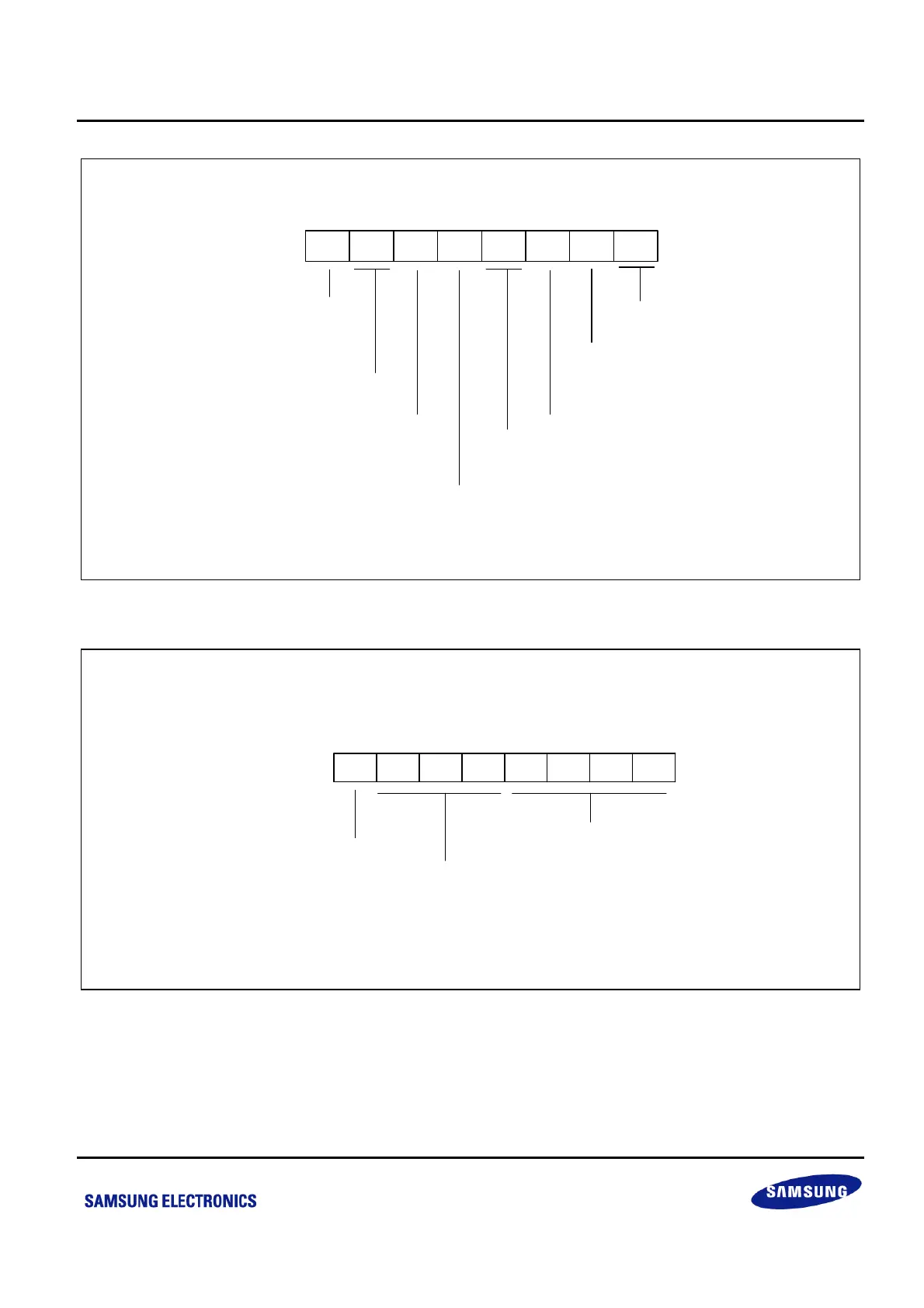

Timer C Control Register (TCCON)

E5H, Set1, Bank1, Reset = 00H, R/W

.7 .6 .5 .4 .3 .2 .1 .0MSB LSB

Timer C Match interrupt pending bit:

0 = No interrupt pending

(clear pending bit when write)

Timer C start/stop bit:

0 = Stop Timer C

1 = Start Timer C

Timer C counter clear bit:

0 = No effect

1 = Clear Timer A counter

(after clearing, return to zero)

Timer C Match interrupt enable bit:

0 = Disable Interupt

1 = Enable interrupt

Timer 0 operation mode selection bit

0 = Two 8-bit timers mode (Timer C/D)

1 = One 16-bit timer mode (Timer 0)

Not used

Not used

Not used

Figure 12-1 Timer 0 Control Register (TCCON)

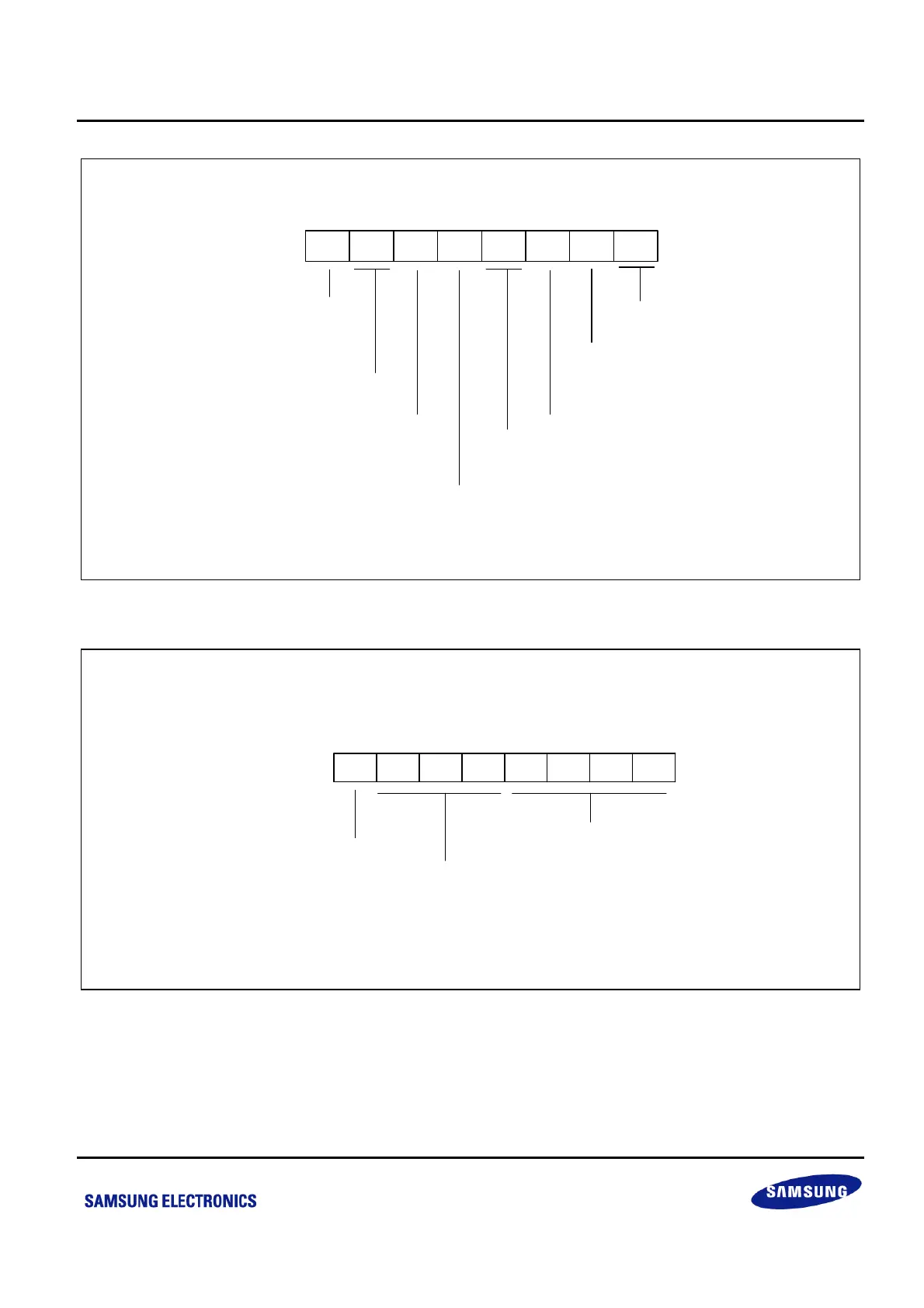

Timer C Prescaler Register (TCPS)

E6H, Set1, Bank1, R/W

LSBMSB.7.6.5.4.3.2.1.0

Reset Value: 00h

Timer C clock source selection bit

0 = Internal clock source

1 = CMP0 output

Not used for S3F84B8

Timer C prescaler bit (TCPSB)

TC CLK = fxx/(2^TCPSB)

NOTE: Pre-scalar values(TCPSB)

above 12

are invalid

Figure 12-2 Timer 0 Prescaler Register (TCPS)

Loading...

Loading...