9-32 Setting the SEL-351P Recloser Control Date Code 990430

SEL-351P Manual Técnico

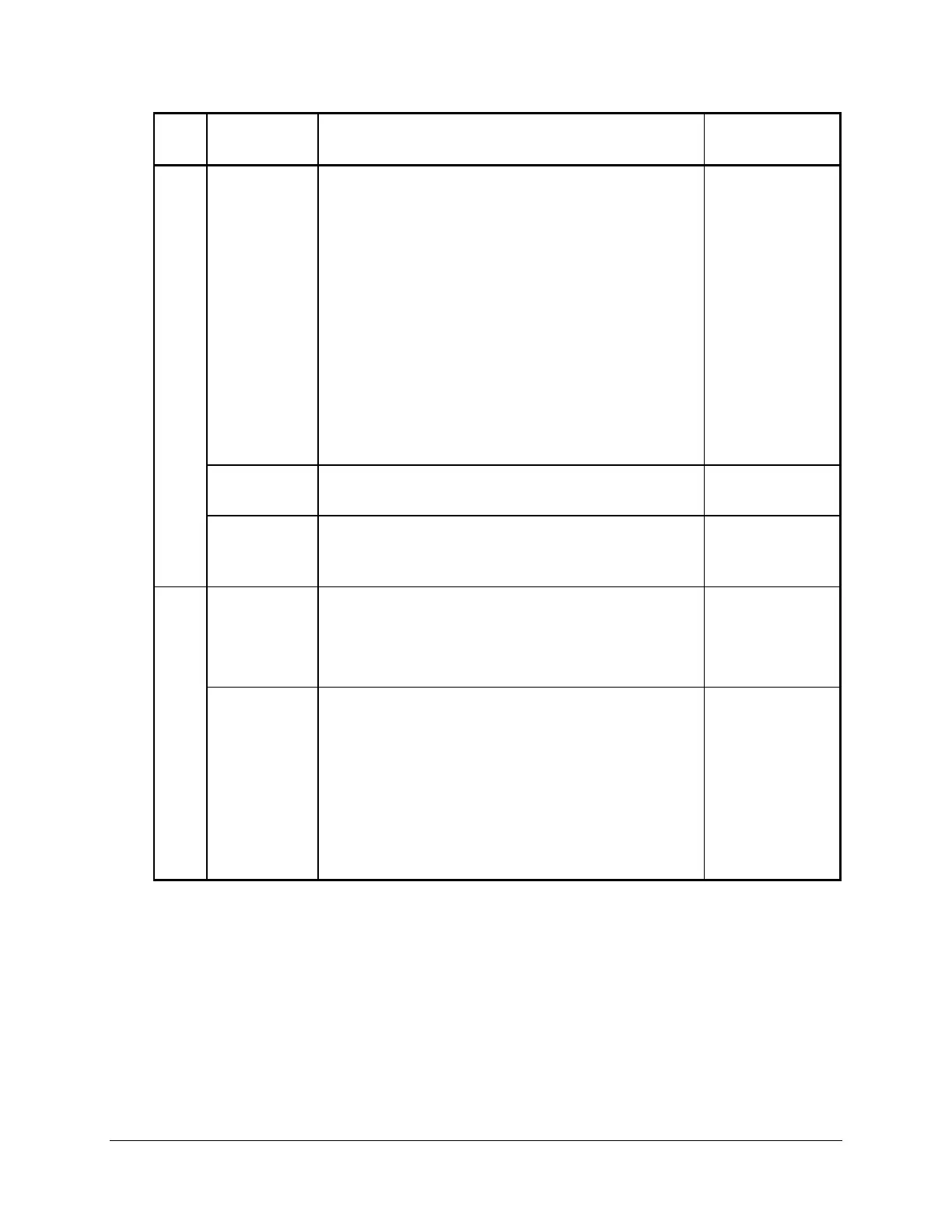

Row

Bit

Definition

Primary

Application

23 81D1T Level 1 definite-time frequency element 81D1T

timed out (derived from 81D1; see Figure 3.28)

Tripping,

Control

81D2T Level 2 definite-time frequency element 81D2T

timed out (derived from 81D2; see Figure 3.28)

81D3T Level 3 definite-time frequency element 81D3T

timed out (derived from 81D3; see Figure 3.28)

81D4T Level 4 definite-time frequency element 81D4T

timed out (derived from 81D4; see Figure 3.28)

81D5T Level 5 definite-time frequency element 81D5T

timed out (derived from 81D5; see Figure 3.28)

81D6T Level 6 definite-time frequency element 81D6T

timed out (derived from 81D6; see Figure 3.28)

VPOLV Positive-sequence polarization voltage valid (see

Figure 4.14)

Testing

LOP Loss-of-potential (see Figure 4.1) Testing, Special

directional

control schemes

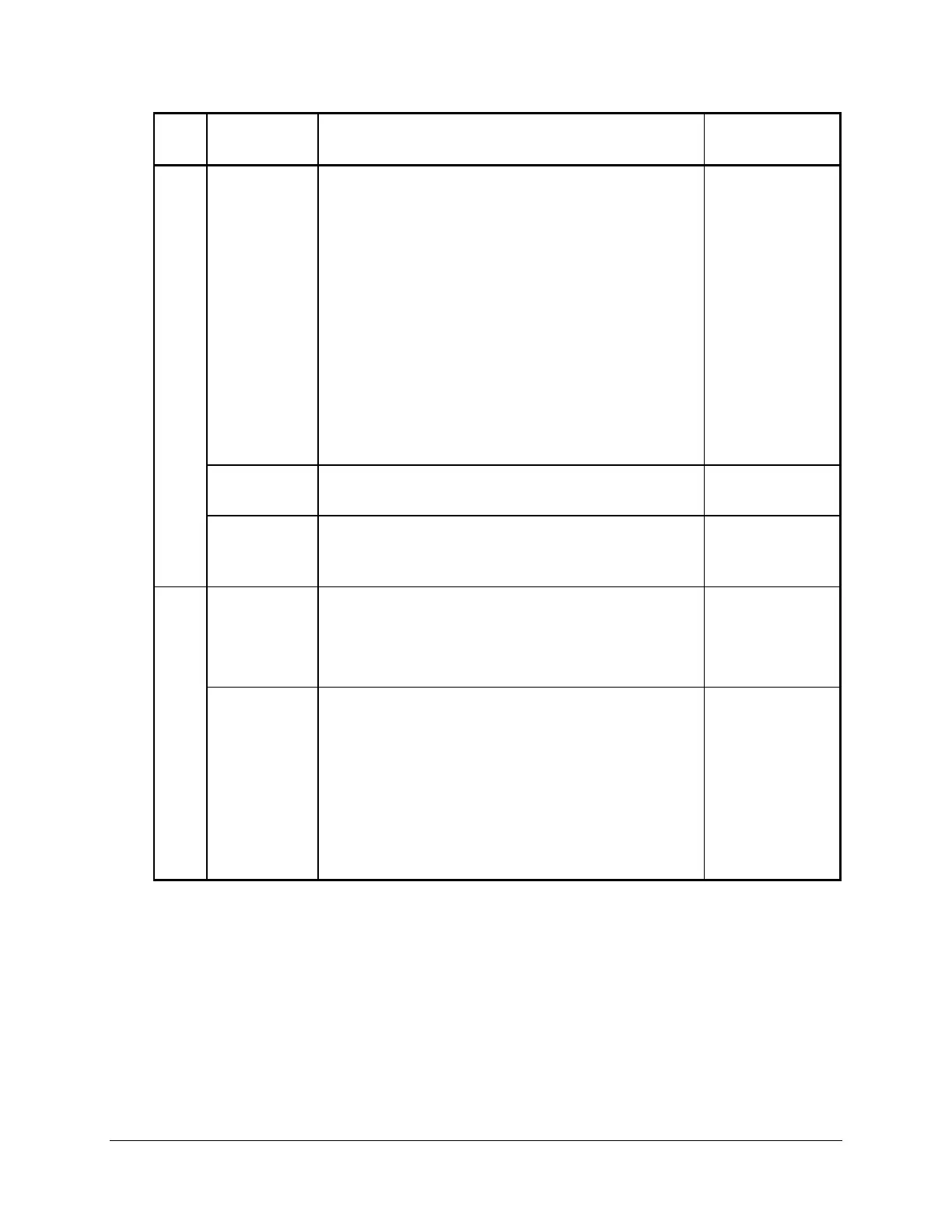

24 50NF

50NR

Forward direction neutral ground overcurrent

threshold exceeded (see Figures 4.4, 4.7, and 4.11)

Reverse direction neutral ground overcurrent

threshold exceeded (see Figures 4.4, 4.7, and 4.11)

Testing

IN106

IN105

IN104

IN103

IN102

IN101

Optoisolated input IN106 asserted (see Figure 7.1)

Optoisolated input IN105 asserted (see Figure 7.1)

Optoisolated input IN104 asserted (see Figure 7.1)

Optoisolated input IN103 asserted (see Figure 7.1)

Optoisolated input IN102 asserted (see Figure 7.1)

Optoisolated input IN101 asserted (see Figure 7.1)

Circuit breaker

status, Control

via optoisolated

inputs

Loading...

Loading...