Addressing Modes Select Bit (AMODE)

5-4

5.2 Addressing Modes Select Bit (AMODE)

To accommodate various types of addressing modes, an addressing mode bit

(AMODE) selects the decoding of the 8-bit field (loc16/loc32). This bit is found

in Status Register 1 (ST1). The addressing modes have been broadly classi-

fied as follows:

- AMODE = 0

This is the default mode on reset and is the mode used by the C28x C/C++

compiler. This mode is not fully compatible to the C2xLP CPU addressing

modes. The data page pointer offset is 6-bits (it is 7-bits on the C2xLP) and

not all of the indirect addressing modes are supported.

- AMODE = 1

This mode contains addressing modes that are fully compatible to the

C2xLP device. The data page pointer offset is increased to 7-bits and all of

the indirect addressing modes available on the C2xLP are supported.

The available addressing modes, for the ”loc16” or ”loc32” field, are summa-

rized in Table 5−1.

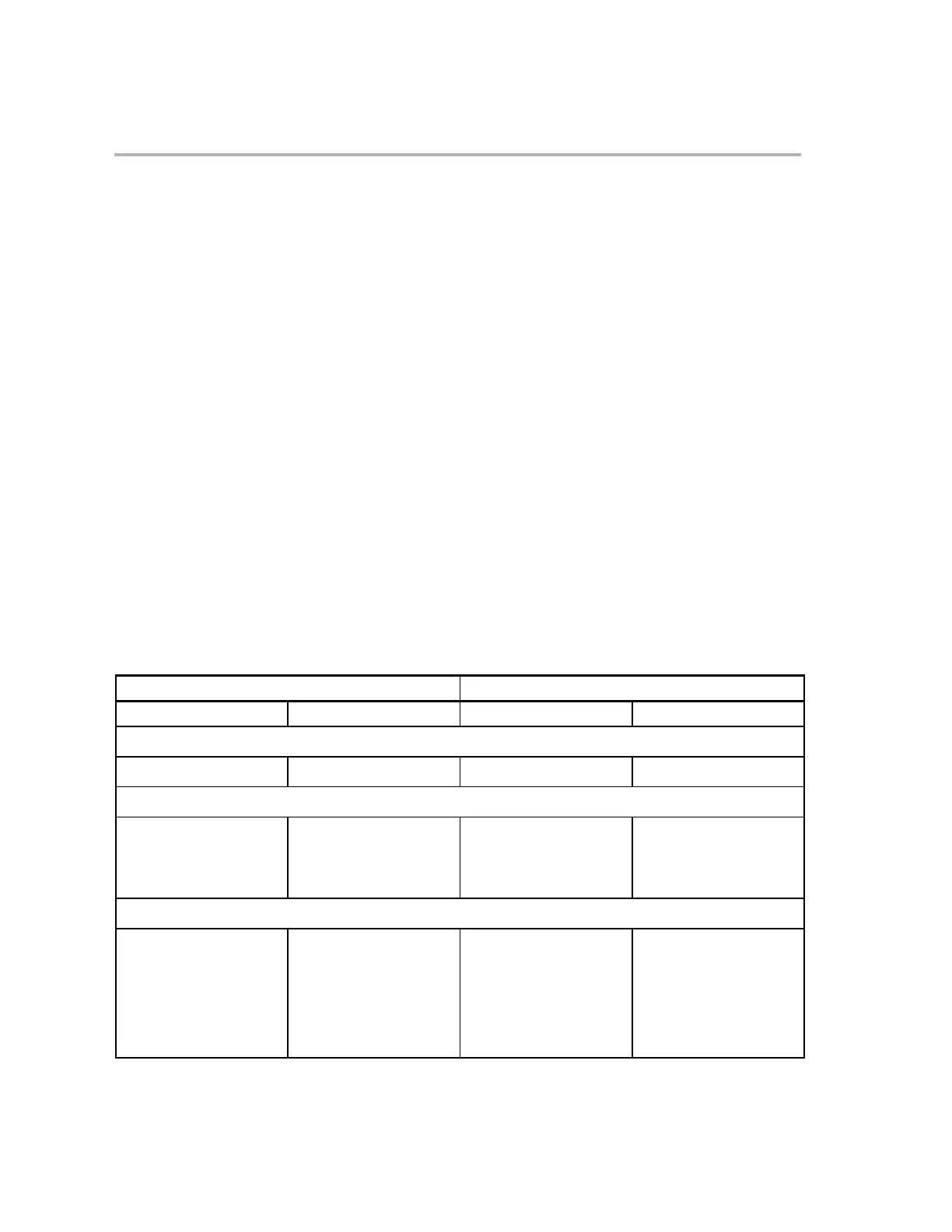

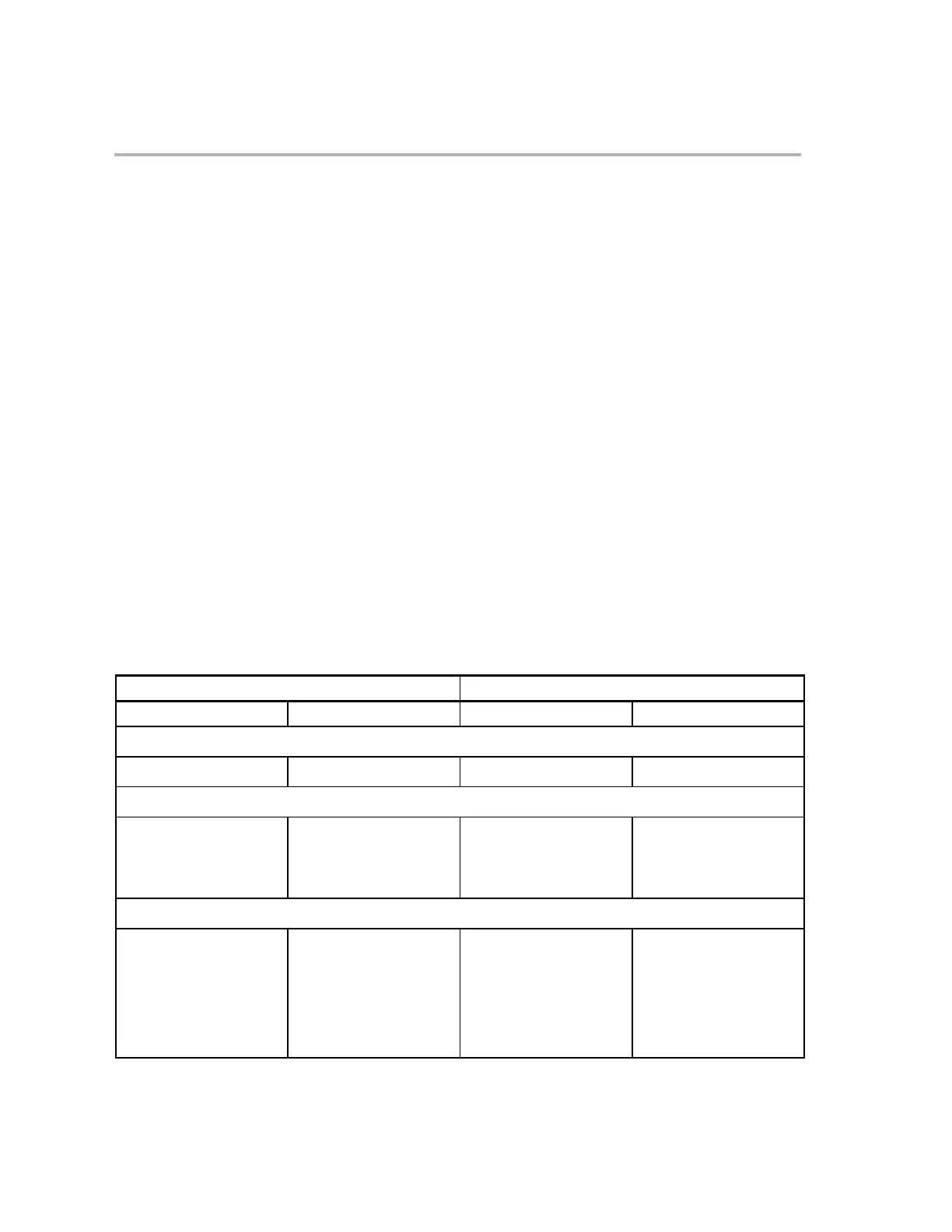

Table 5−1. Addressing Modes for “loc16” or “loc32”

AMODE = 0 AMODE = 1

8-Bit Decode ”loc16/loc32” Syntax 8-Bit Decode ”loc16/loc32” Syntax

Direct Addressing Modes (DP):

0 0 III III @6bit 0 I III III @@7bit

Stack Addressing Modes (SP):

0 1 III III

1 0 111 101

1 0 111 110

*−SP[6bit]

*SP++

*−−SP

1 0 111 101

1 0 111 110

*SP++

*−−SP

C28x Indirect Addressing Modes (XAR0 to XAR7):

1 0 000 AAA

1 0 001 AAA

1 0 010 AAA

1 0 011 AAA

1 1 III AAA

*XARn++

*−−XARn

*+XARn[AR0]

*+XARn[AR1]

*+XARn[3bit]

1 0 000 AAA

1 0 001 AAA

1 0 010 AAA

1 0 011 AAA

*XARn++

*−−XARn

*+XARn[AR0]

*+XARn[AR1]

Loading...

Loading...