Register Figures

A-9Register Quick Reference

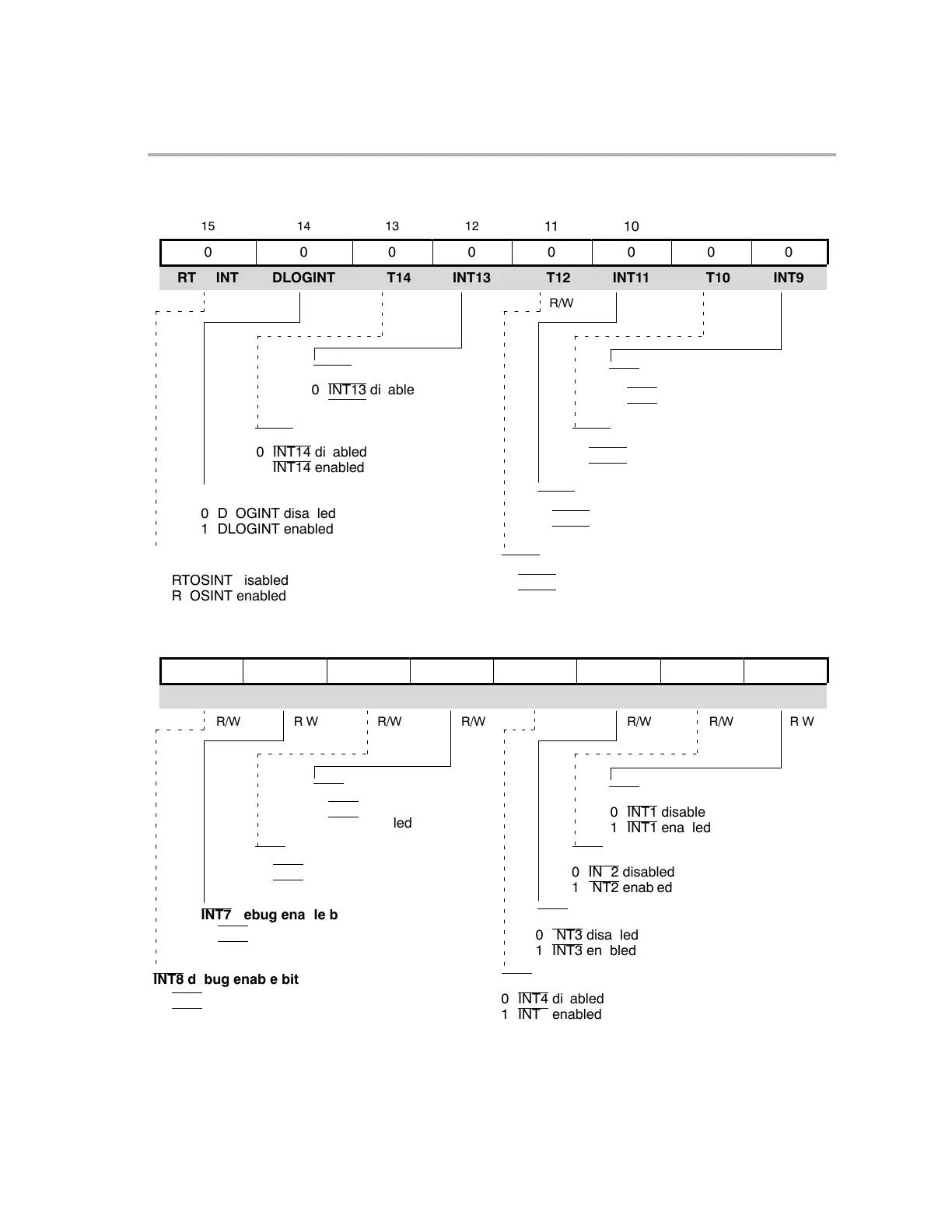

Figure A−6. Debug interrupt enable register (DBGIER)

15

14

13

12

11

10

9

8

0

0

0

0

0

0

0

0

RTOSINT DLOGINT INT14 INT13 INT12 INT11 INT10 INT9

R/W

0

1

RTOSINT disabled

RTOSINT enabled

0

1

DLOGINT disabled

DLOGINT enabled

0

1

INT14

disabled

INT14

enabled

0

1

INT13 disabled

INT13

enabled

0

1

INT12

disabled

INT12

enabled

0

1

INT11

disabled

INT11

enabled

0

1

INT10 disabled

INT10

enabled

0

1

INT9

disabled

INT9

enabled

R/W R/W R/WR/WR/W R/W R/W

RTOSINT debug enable bit

DLOGINT debug enable bit

INT14

debug enable bit

INT13

debug enable bit

INT12 debug enable bit

INT11

debug enable bit

INT10

debug enable bit

INT9

debug enable bit

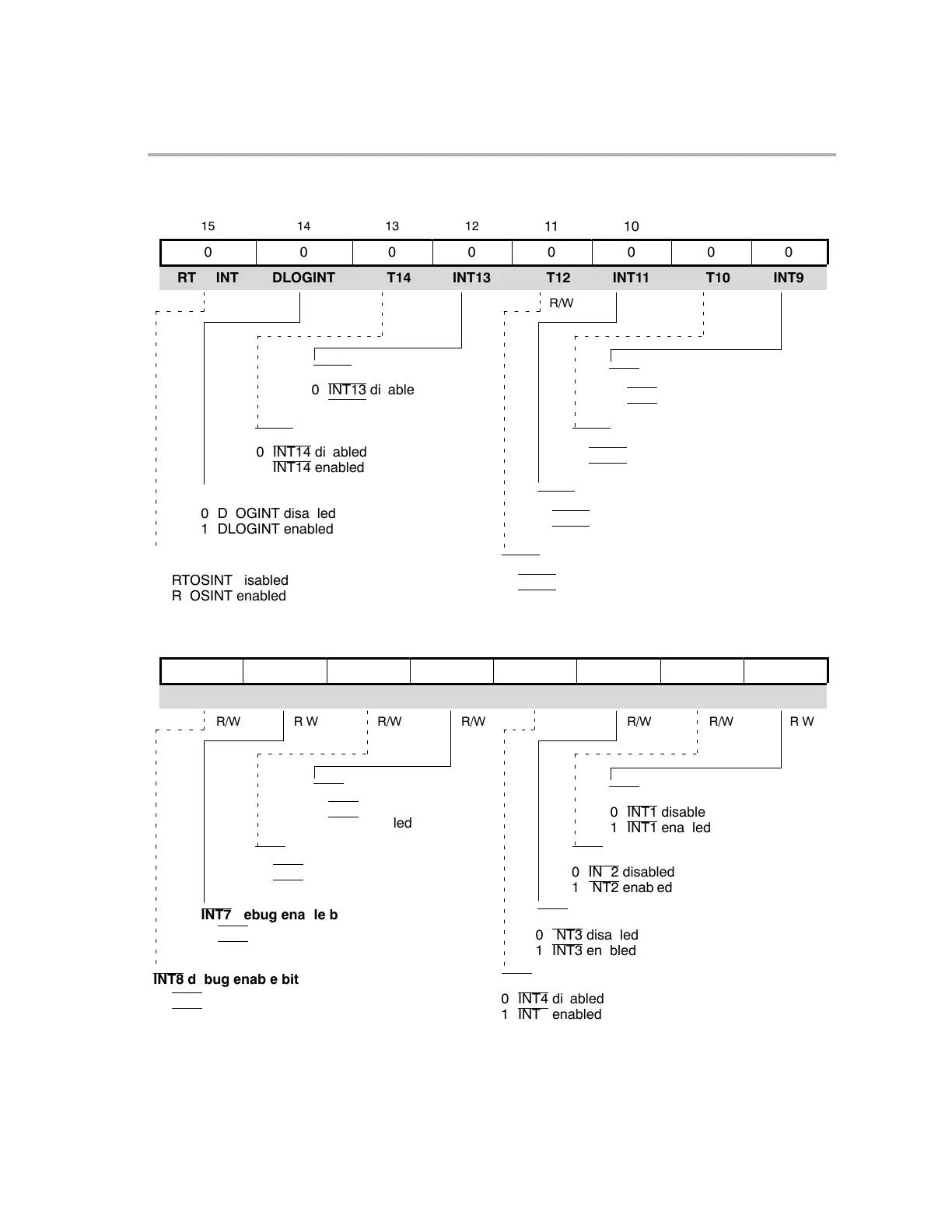

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

0

INT8 INT7 INT6 INT5 INT4 INT3 INT2 INT1

R/W

0

1

INT8 disabled

INT8

enabled

0

1

INT7 disabled

INT7

enabled

0

1

INT6

disabled

INT6

enabled

0

1

INT5 disabled

INT5

enabled

0

1

INT4

disabled

INT4

enabled

0

1

INT3

disabled

INT3

enabled

0

1

INT2 disabled

INT2

enabled

0

1

INT1

disabled

INT1

enabled

R/W R/W R/WR/WR/W R/W R/W

INT8 debug enable bit

INT7

debug enable bit

INT6

debug enable bit

INT5

debug enable bit

INT4 debug enable bit

INT3

debug enable bit

INT2

debug enable bit

INT1

debug enable bit

Note: For more details about the DBGIER, see section 3.3.2 on page 3-8.

Loading...

Loading...