Execution Control Modes

7-8

The CPU can service all interrupts in this state. When an interrupt occurs

simultaneously with a debug event, the debug event has priority; however,

if interrupt processing began before the debug event occurred, the debug

event cannot be processed until the interrupt service routine begins.

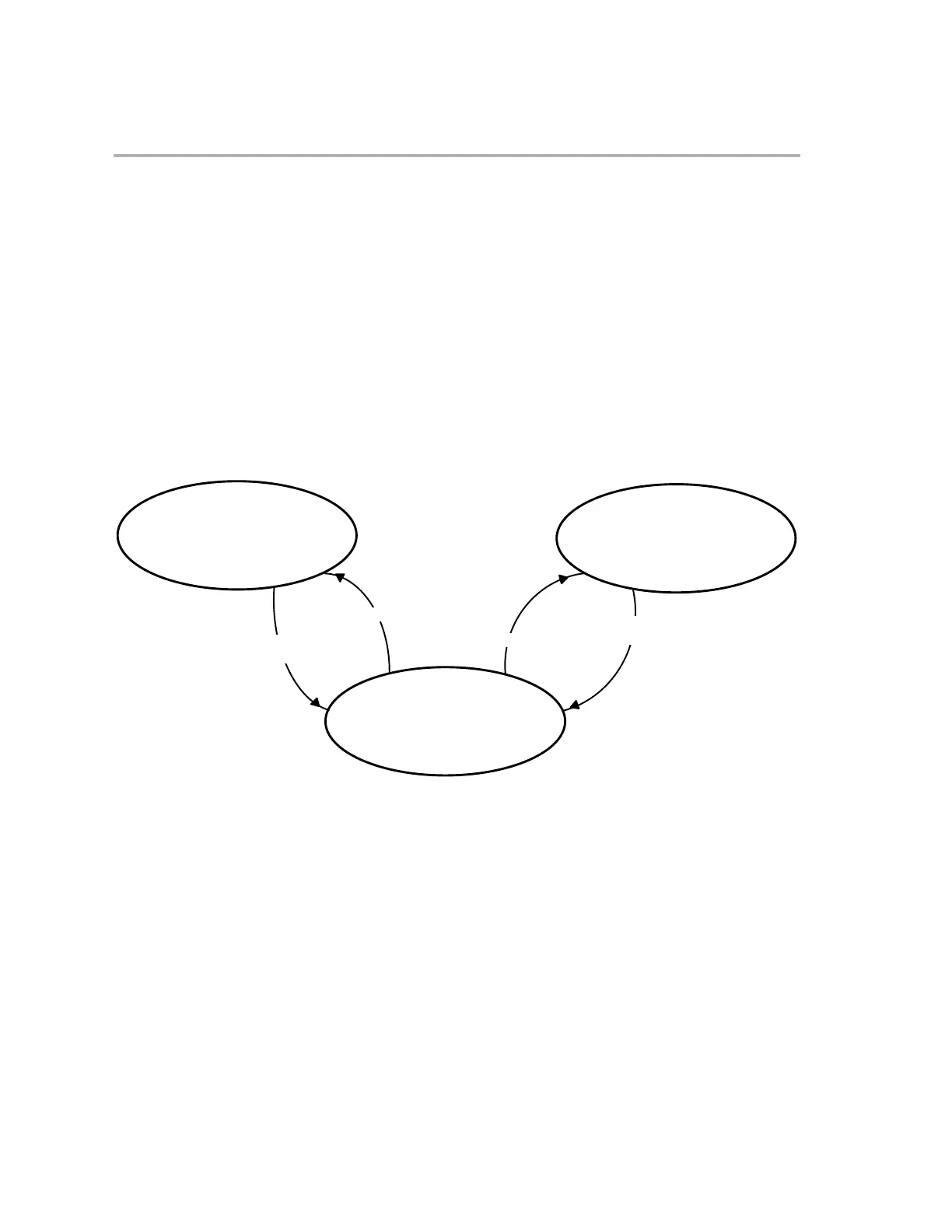

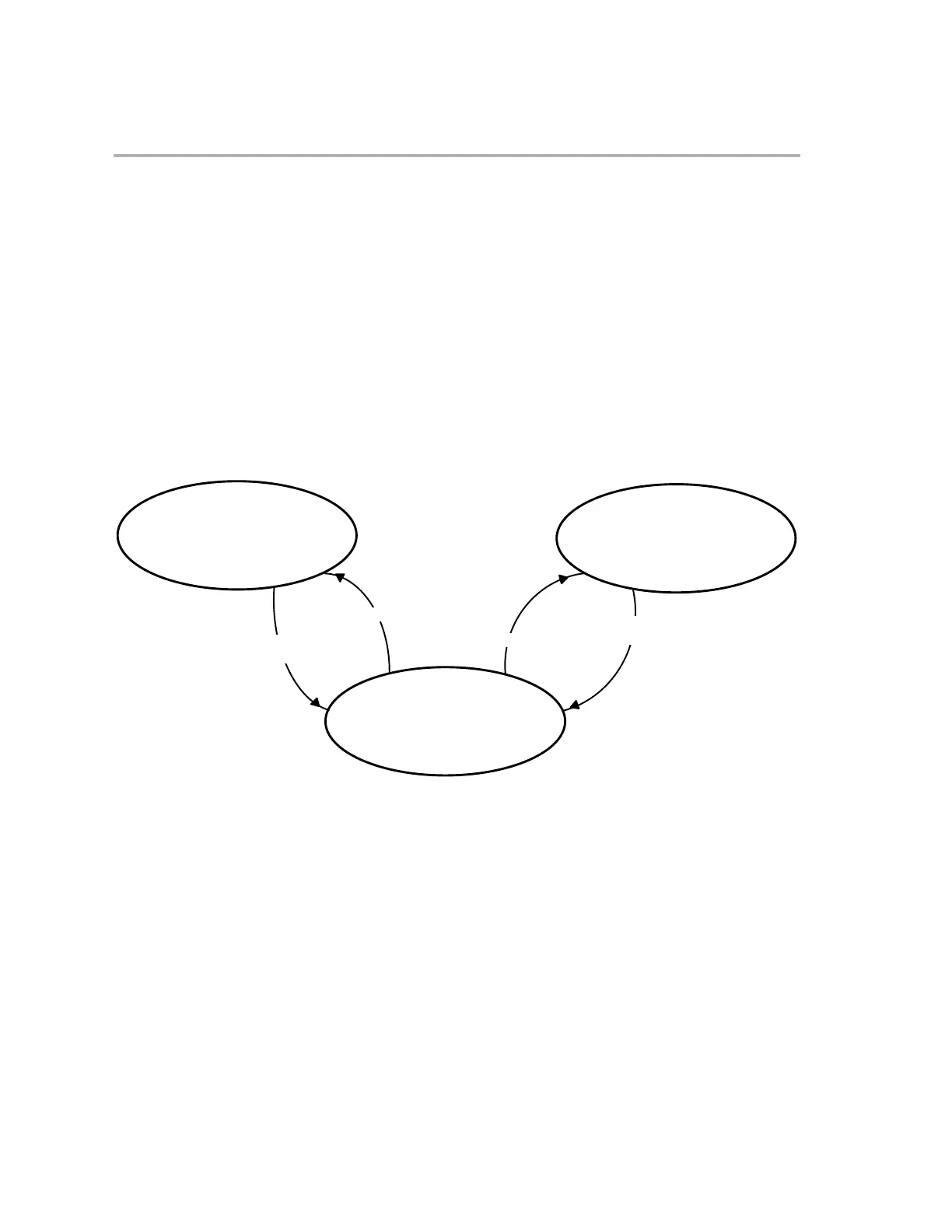

Figure 7−2 illustrates the relationship among the three states. Notice that the

C28x cannot pass directly between the single-instruction and run states. No-

tice also that the CPU can be observed only in the debug-halt state. In practical

terms, this means the contents of CPU registers and memory are not updated

in the debugger display in the single-instruction state or the run state. Mask-

able interrupts occurring in any state are latched in the interrupt flag register

(IFR).

Figure 7−2. Stop Mode Execution States

Single-instruction state

Run state

Debugger command

Debugger command

After executing

one instruction

Debugger command,

breakpoint, or analysis stop

Debug-halt state

Can service an interrupt

if RUN 1 used

†

Cannot observe CPU

Can service interrupts

Cannot observe CPU

Cannot service interrupts

Can observe CPU

†

If you use a RUN 1 command to execute a single instruction, an interrupt can be serviced in the single-instruction state. If you use

a STEP 1 command for the same purpose, an interrupt cannot be serviced.

Loading...

Loading...