Register Figures

A-5Register Quick Reference

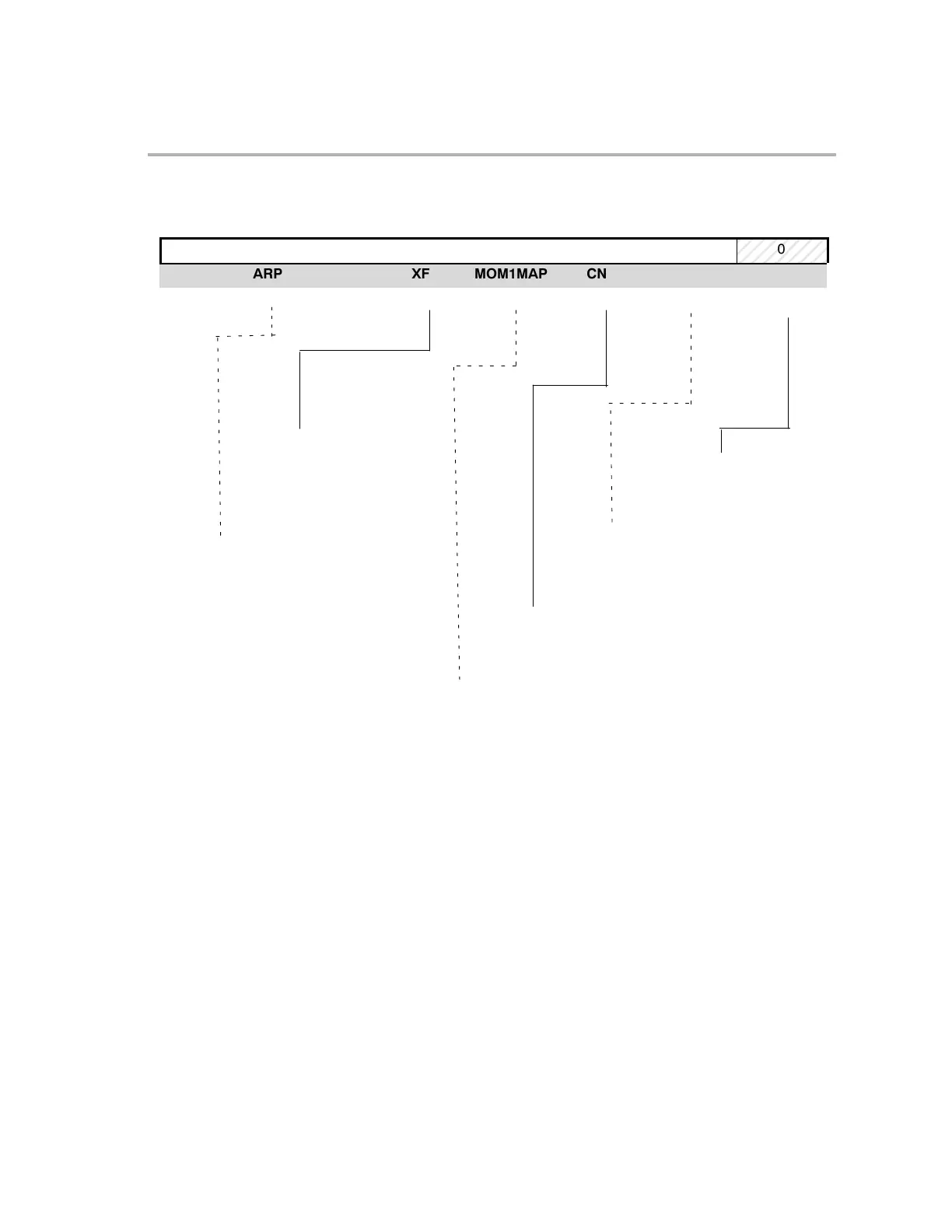

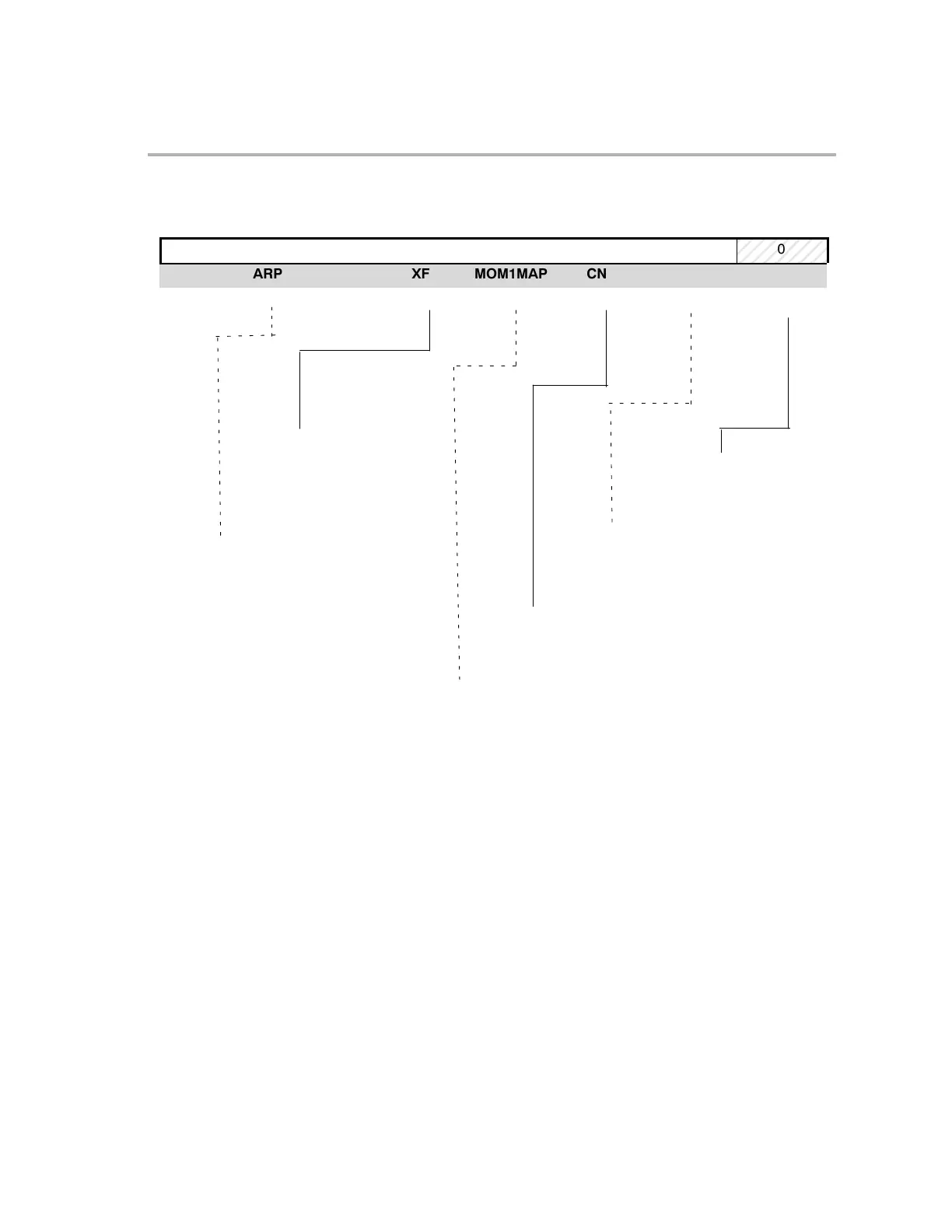

Figure A−2. Status register ST1, Bits15−8

15 14 13 12 11 10 9 8

0 0 0 0 0 0 0

ÉÉÉ

0

ARP XF MOM1MAP CNF OBJMODE AMODE

R/W R/WR/WR/W

R

0

1

XF status bit

0

1

Address mode bit

0

1

Object compatibility mode bit

C2xLP-mapping mode bit

PAGE0 stack addressing mode

PAGE0 direct addressing mode

0

1

0

1

M0 and M1 mapping mode bit

Auxiliary register pointer

XAR0 selected

XAR1 selected

XAR2 selected

XAR3 selected

XAR4 selected

XAR5 selected

XAR6 selected

XAR7 selected

0

0

1

1

0

0

1

1

0

0

0

0

1

1

1

1

0

1

0

1

0

1

0

1

R/W

C27x compatible map

C28x/C2xLP compatible map

C28x/C27x processing mod

C2xLP addressing modes

XFS output signal low

XFS output signal is high

M0 is 0−3FF data, 400−7FF pro-

gram

M0 is 0−3FF data and program

SP starts at 0x400.

Loading...

Loading...