QMPYXUL P,XT,loc32

6-309

QMPYXUL P,XT,loc32 Signed X Unsigned 32-bit Multiply (Upper Half)

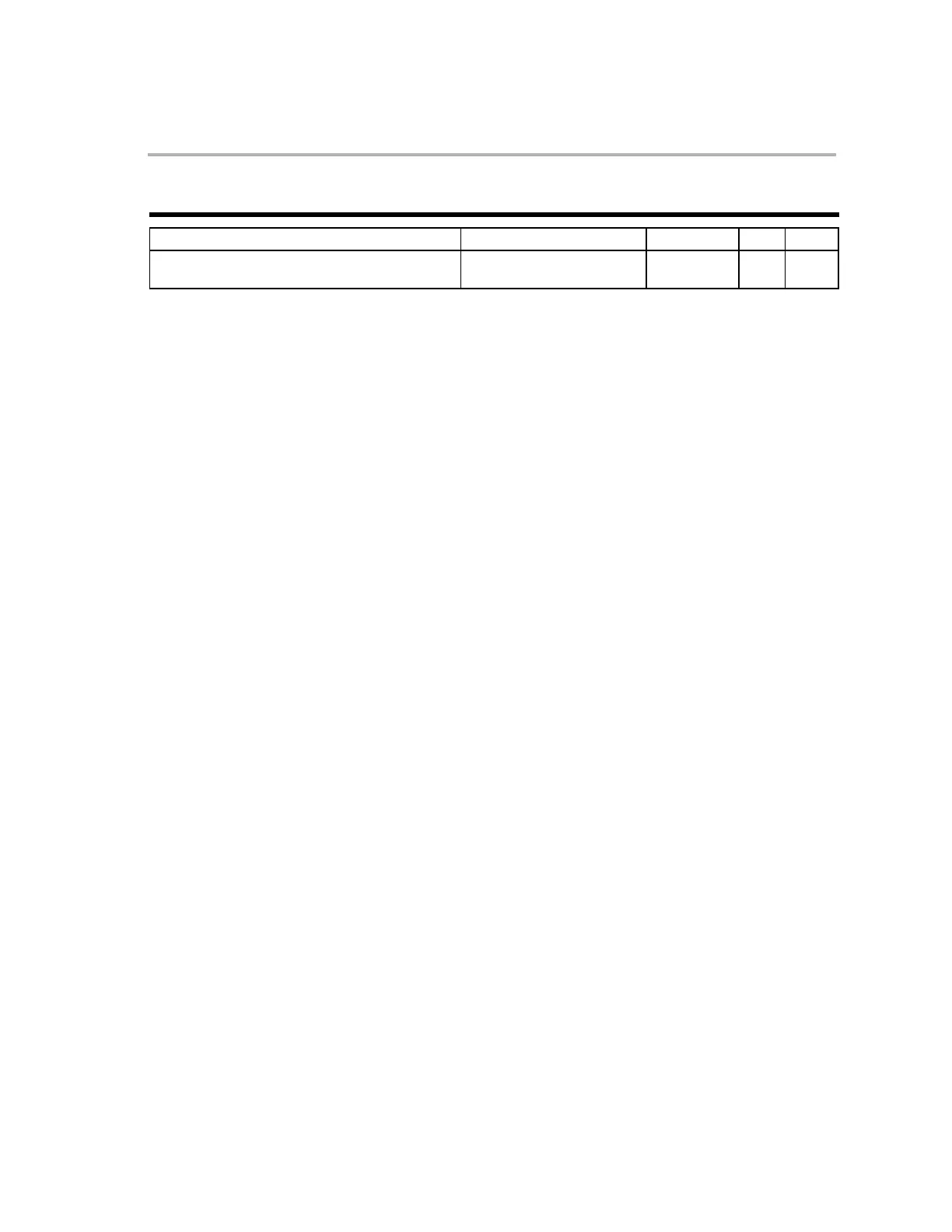

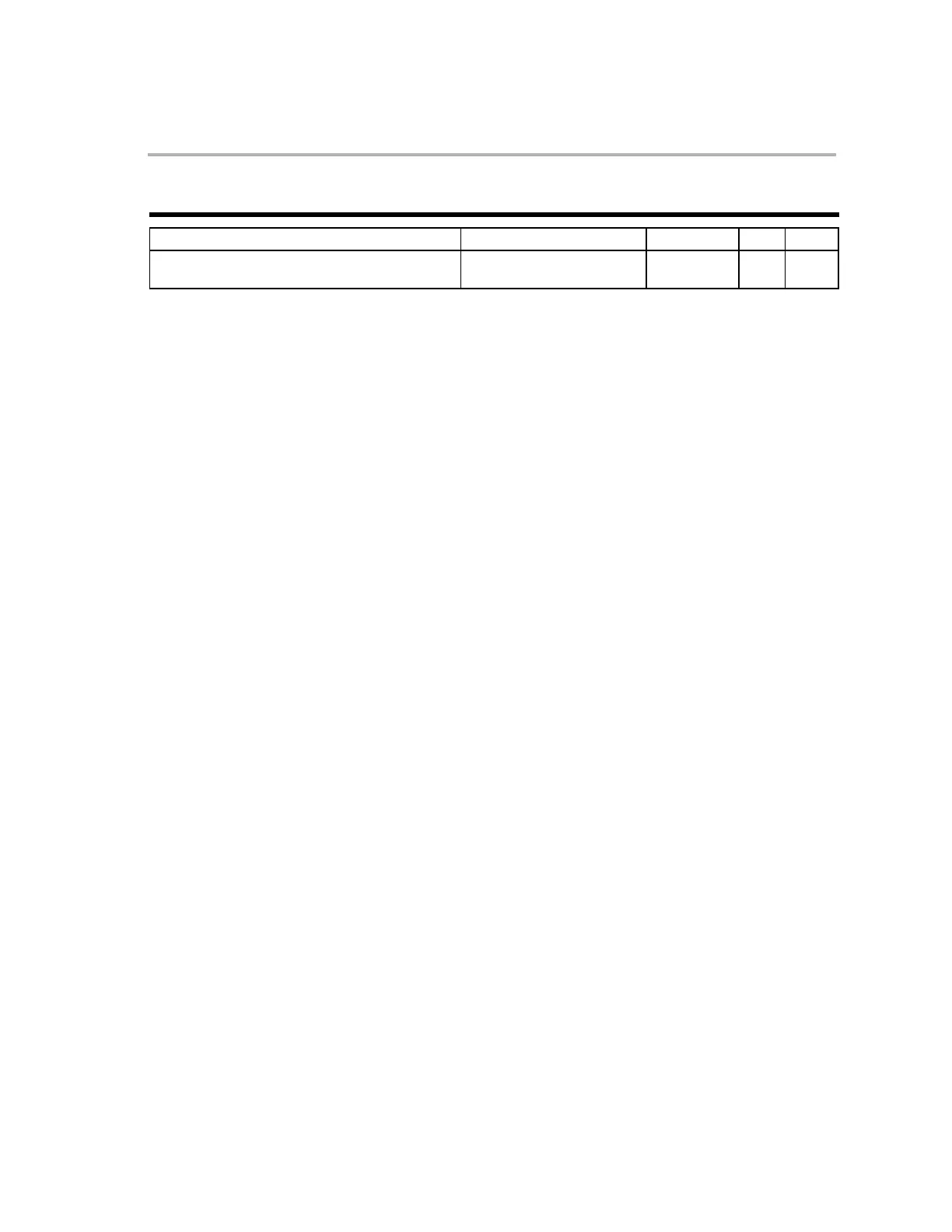

SYNTAX OPTIONS OPCODE OBJMODE RPT CYC

QMPYXUL P,XT,loc32 0101 0110 0100 0010

0000 0000 LLLL LLLL

1 − 1

Operands P Product register

XT Multiplicand register

loc32 Addressing mode (see Chapter 5)

Description Multiply the signed 32-bit content of the XT register by the unsigned 32-bit

content of the location pointed to by the “loc32” addressing mode and store

the upper 32−bits of the 64-bit result in the P register:

P = (signed XT * unsigned [loc32]) >> 32;

Flags and

Modes

None

Repeat This instruction is not repeatable. If this instruction follows the RPT

instruction, it resets the repeat counter (RPTC) and executes only once.

Example

; Calculate signed result: Y64 = (M64*X64) >> 64 + B64

; Y64 = Y1:Y0, M64 = M1:M0, X64 = X1:X0, B64 = B1:B0

MOVL XT,@X1 ; XT = X1

QMPYXUL P,XT,@M0 ; P = high 32−bits of (uns M0 * sign X1)

MOV @T,#32 ; T = 32

LSL64 ACC:P,T ; ACC:P = ACC:P << T

ASR64 ACC:P,T ; ACC:P = ACC:P >> T

MOVL @XAR4,P ; XAR5:XAR4 = ACC:P

MOVL @XAR5,ACC

MOVL XT,@M1 ; XT = M1

QMPYXUL P,XT,@X0 ; P = high 32−bits of (sign M1 * uns X0)

MOV @T,#32 ; T = 32

LSL64 ACC:P,T ; ACC:P = ACC:P << T

ASR64 ACC:P,T ; ACC:P = ACC:P >> T

MOVL @XAR6,P ; XAR7:XAR6 = ACC:P

MOVL @XAR7,ACC

IMPYL P,XT,@X1 ; P = low 32−bits of (sign M1 * sign X1)

QMPYL ACC,XT,@X1 ; ACC = high 32−bits of (sign M1 * sign X1)

ADDUL P,@XAR4 ; ACC:P = ACC:P + XAR5:XAR4

ADDCL ACC,@XAR5

ADDUL P,@XAR6 ; ACC:P = ACC:P + XAR7:XAR6

ADDCL ACC,@XAR7

ADDUL P,@B0 ; ACC:P = ACC:P + B64

ADDCL ACC,@B1

MOVL @Y0,P ; Store result into Y64

MOVL @Y1,ACC

Loading...

Loading...