SUB ACC,loc16 <<T

6-335

SUB ACC,loc16 <<T Subtract Shifted Value From Accumulator

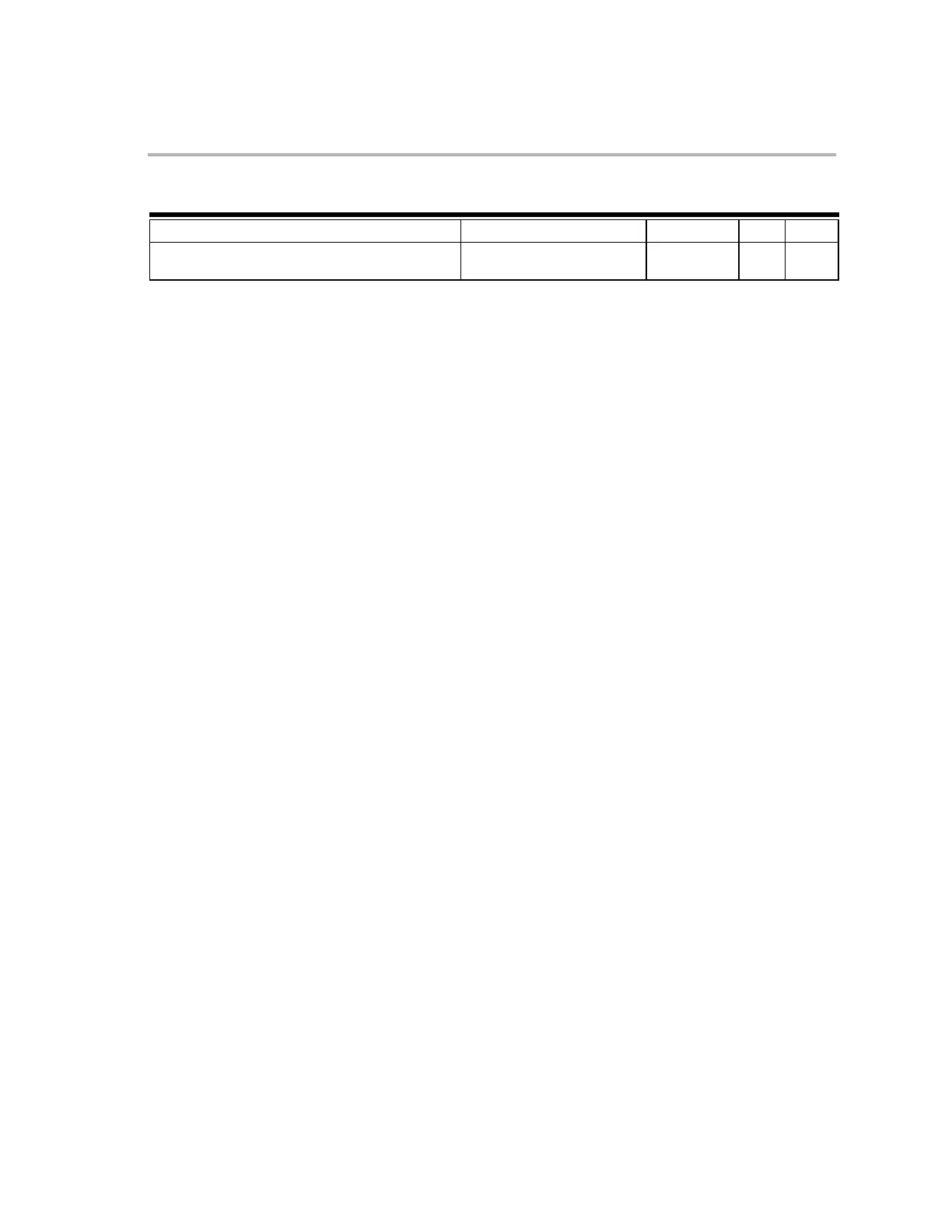

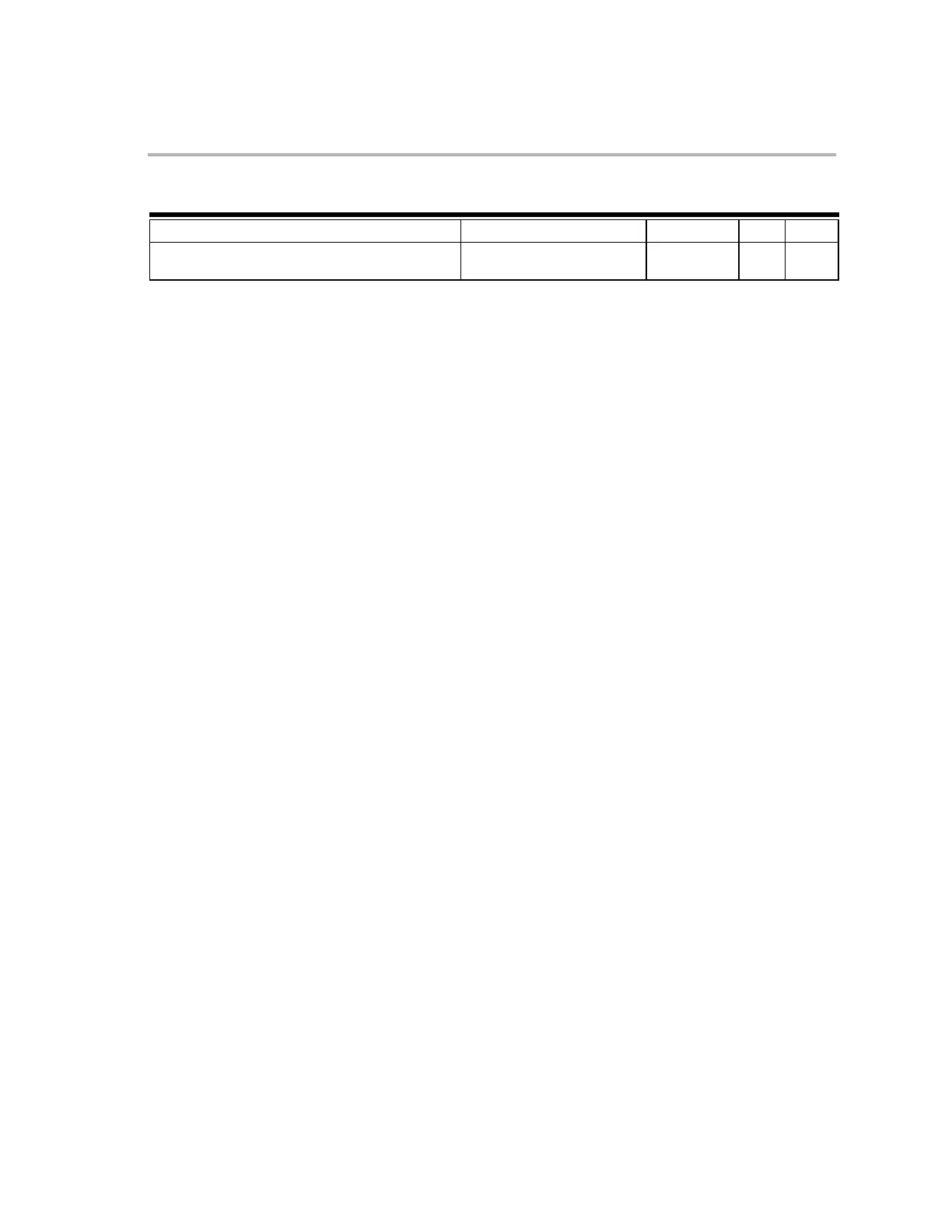

SYNTAX OPTIONS OPCODE OBJMODE RPT CYC

SUB ACC,loc16 <<T 0101 0110 0010 0111

0000 0000 LLLL LLLL

1 Y N+1

Operands ACC Accumulator register

loc16 Addressing mode (see Chapter 5)

T Upper 16−bits of the multiplicand register, XT(31:16)

Description Subtract from the ACC register the left−shifted contents of the 16-bit location

pointed to by the “loc16” addressing mode. The shift value is specified by the

four least significant bits of the T register, T(3:0) = shift value = 0..15. Higher

order bits are ignored. The shifted value is sign extended if sign extension

mode is turned on (SXM=1) else the shifted value is zero extended (SXM=0).

The lower bits of the shifted value are zero filled:

if(SXM = 1) // sign extension mode enabled

ACC = ACC − S:[loc16] << T(3:0);

else // sign extension mode disabled

ACC = ACC − 0:[loc16] << T(3:0);

Flags and

Modes

Z

After the subtraction, the Z flag is set if the ACC value is zero, else Z is

cleared.

N

After the subtraction, the N flag is set if bit 31 of the ACC is 1, else N is

cleared.

C

If the subtraction generates a borrow, C is cleared; otherwise C is set.

V

If an overflow occurs, V is set; otherwise V is not affected.

OVC

If(OVM = 0, disabled) then if the operation generates a positive overflow,

then the counter is incremented and if the operation generates a negative

overflow, then the counter is decremented. If(OVM = 1, enabled) then the

counter is not affected by the operation.

SXM

If sign extension mode bit is set; then the 16-bit operand, addressed by the

”loc16” field, will be sign extended before the addition. Else, the value will be

zero extended.

OVM

If overflow mode bit is set; then the ACC value will saturate maximum

positive (0x7FFF FFFF) or maximum negative (0x8000 0000) if the

operation overflowed.

Repeat If this operation is repeated, then the instruction will be executed N+1 times.

The state of the Z, N, C flags will reflect the final result. The V flag will be set if

an intermediate overflow occurs. The OVC flag will count intermediate

overflows, if overflow mode is disabled.

Loading...

Loading...