TBIT loc16,T

6-360

TBIT loc16,T Test Bit Specified by Register

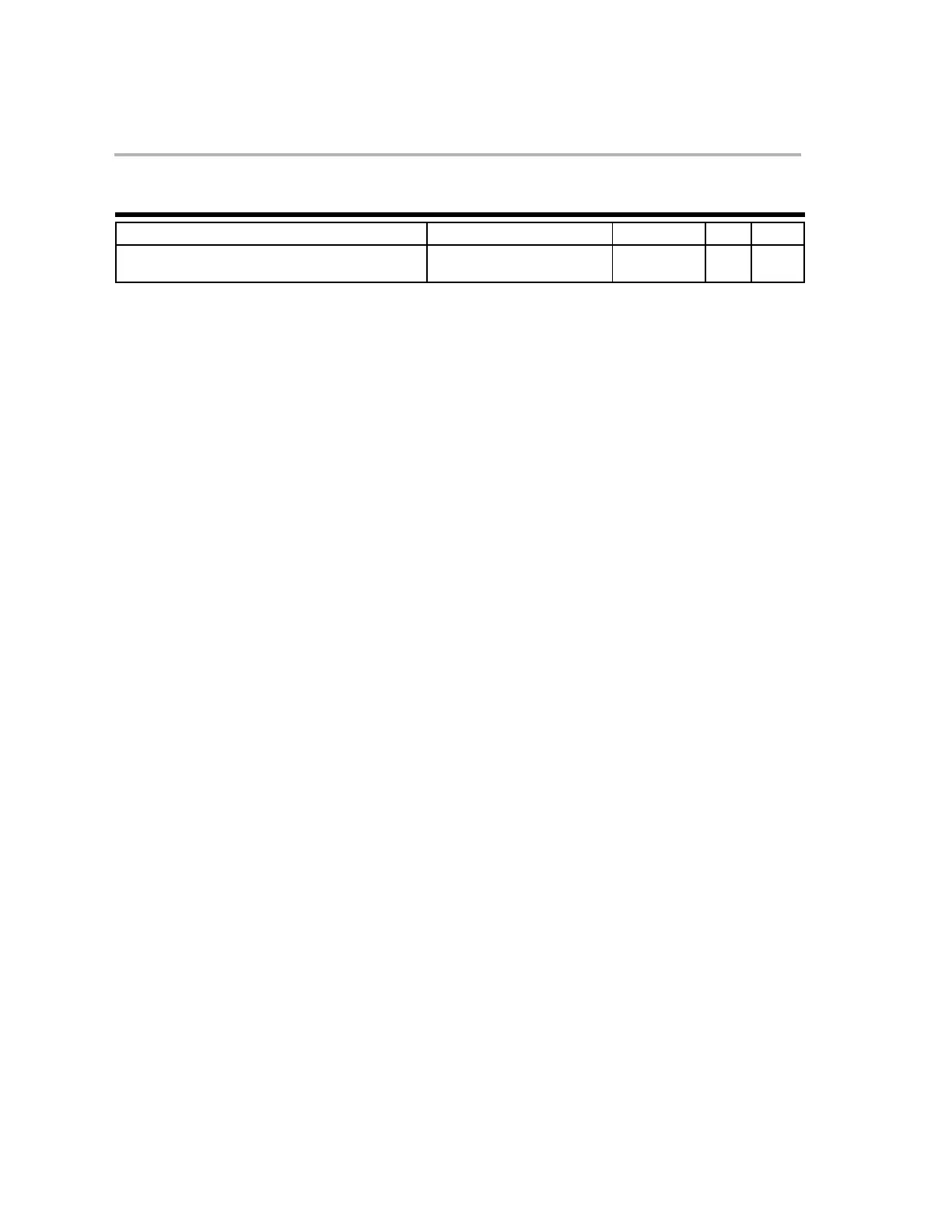

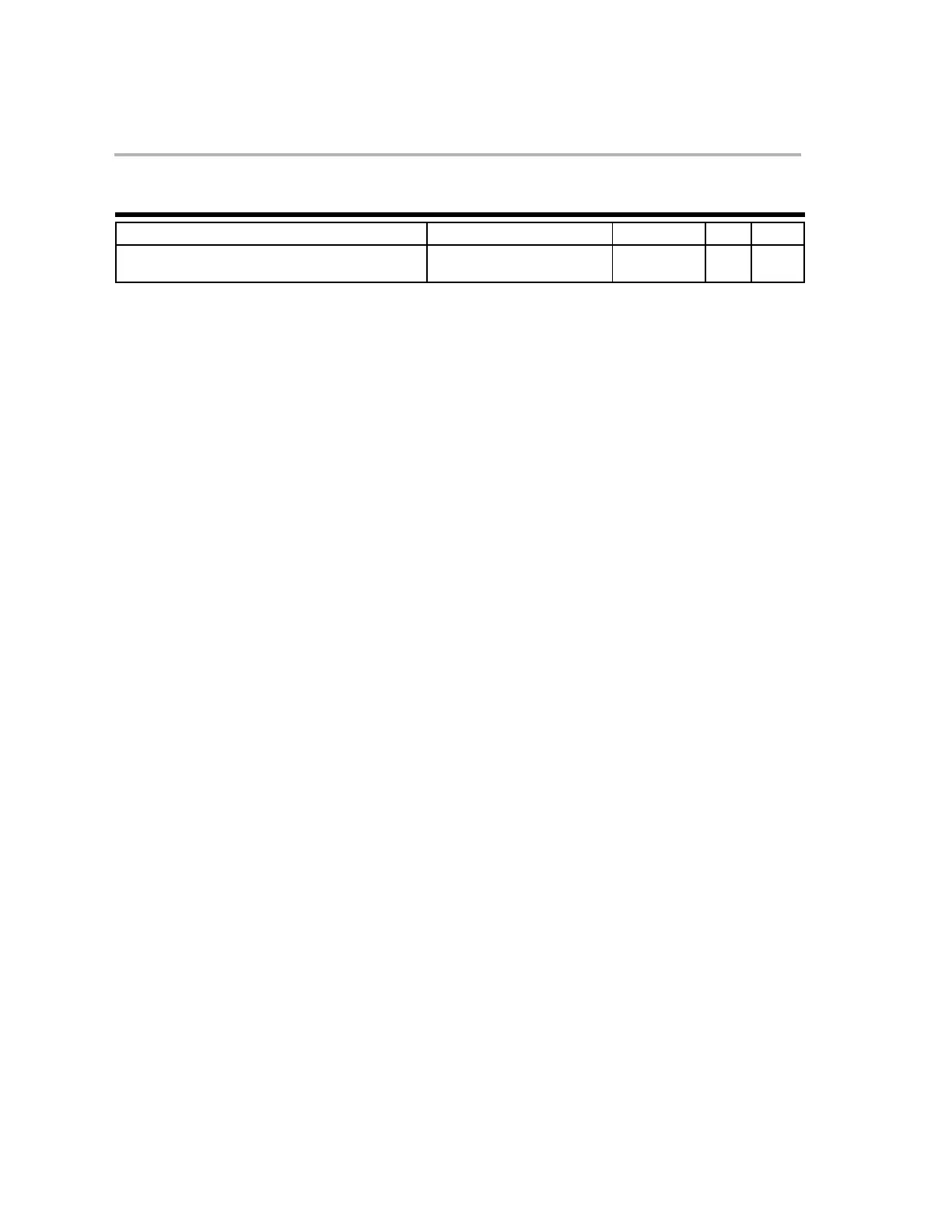

SYNTAX OPTIONS OPCODE OBJMODE RPT CYC

TBIT loc16,T 0101 0110 0010 0101

0000 0000 LLLL LLLL

1 − 1

Operands

loc16 T

Addressing mode (see Chapter 5)

Upper 16 bits of the multiplicand register (XT)

Description Test the bit specified by the four least significant bits of the T register,

T(3:0) = 0…15 of the data value in the location pointed to by the “loc16”

addressing mode. Upper bits of the T register are ignored:

bit = 15 − T(3:0);

TC = [loc16(bit)];

A value of 15 in the T register corresponds to bit 0 (least significant bit). A

value of 0 in the T register corresponds to bit 15 (most significant bit). The

upper 12 bits of the T register are ignored.

Flags and

Modes

TC If the bit tested is 1, TC is set; if the bit tested is 0, TC is cleared.

Repeat This instruction is not repeatable. If this instruction follows the RPT

instruction, it resets the repeat counter (RPTC) and executes only once.

Example

; if( VarA.VarB = 1 )

; VarC.Bit6 = 1;

; else

; VarC.Bit6 = 0;

MOV T,@VarB ; Load T with bit value in VarB

ADD @T,#15 ; Reverse order of bit testing

TBIT @VarA,T ; Test bit of VarA selected by VarB

SB $10,NTC ; Branch if TC = 0

TSET @VarB,#6 ; Set bit 6 of VarB contents

SB $20,UNC ; Branch unconditionally

$10: ;

TCLR @VarB,#6 ; Clear bit 6 of VarB contents

$20: ;

Loading...

Loading...