Data Logging

7-24

(DMA_CNTRL). EVT_CNTRL is described in Table 7−5 (page 7-26),

and DMA_CNTRL is described in Table 7−4 (page 7-25).

Note:

The application must not read from the end address of the buffer during the

data logging operation. When the end address appears on the address bus,

the C28x ends the transfer.

4) Execute the EDIS instruction to disable access to emulation registers.

See Table 7−4 and Table 7−5 on the following pages for descriptions of the

registers associated with data logging.

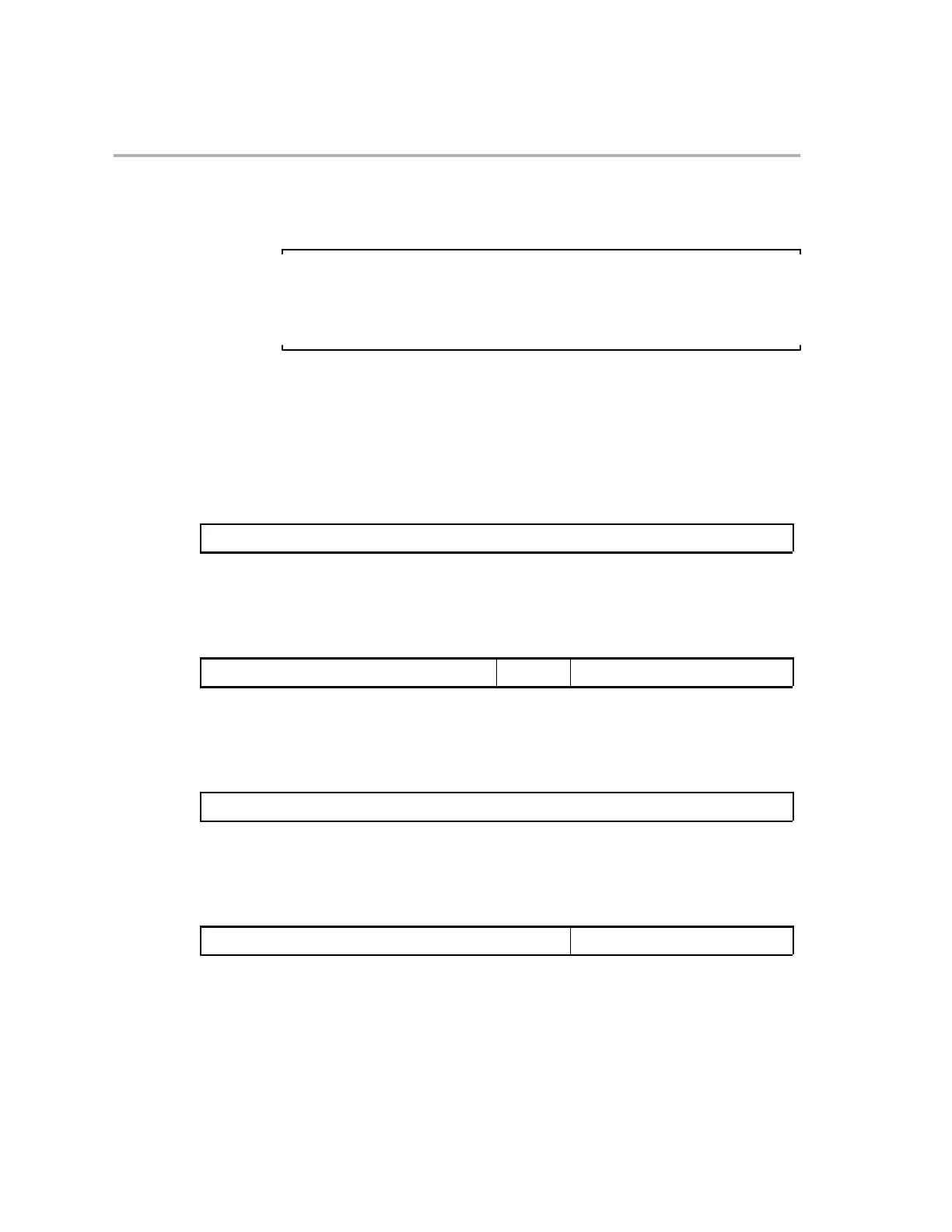

Figure 7−6. ADDRL (at Data-Space Address 00 0838

16

)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

16 LSBs of transfer address

Figure 7−7. ADDRH (at Data-Space Address 00 0839

16

)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Word counter

Reserved 6 MSBs of transfer address

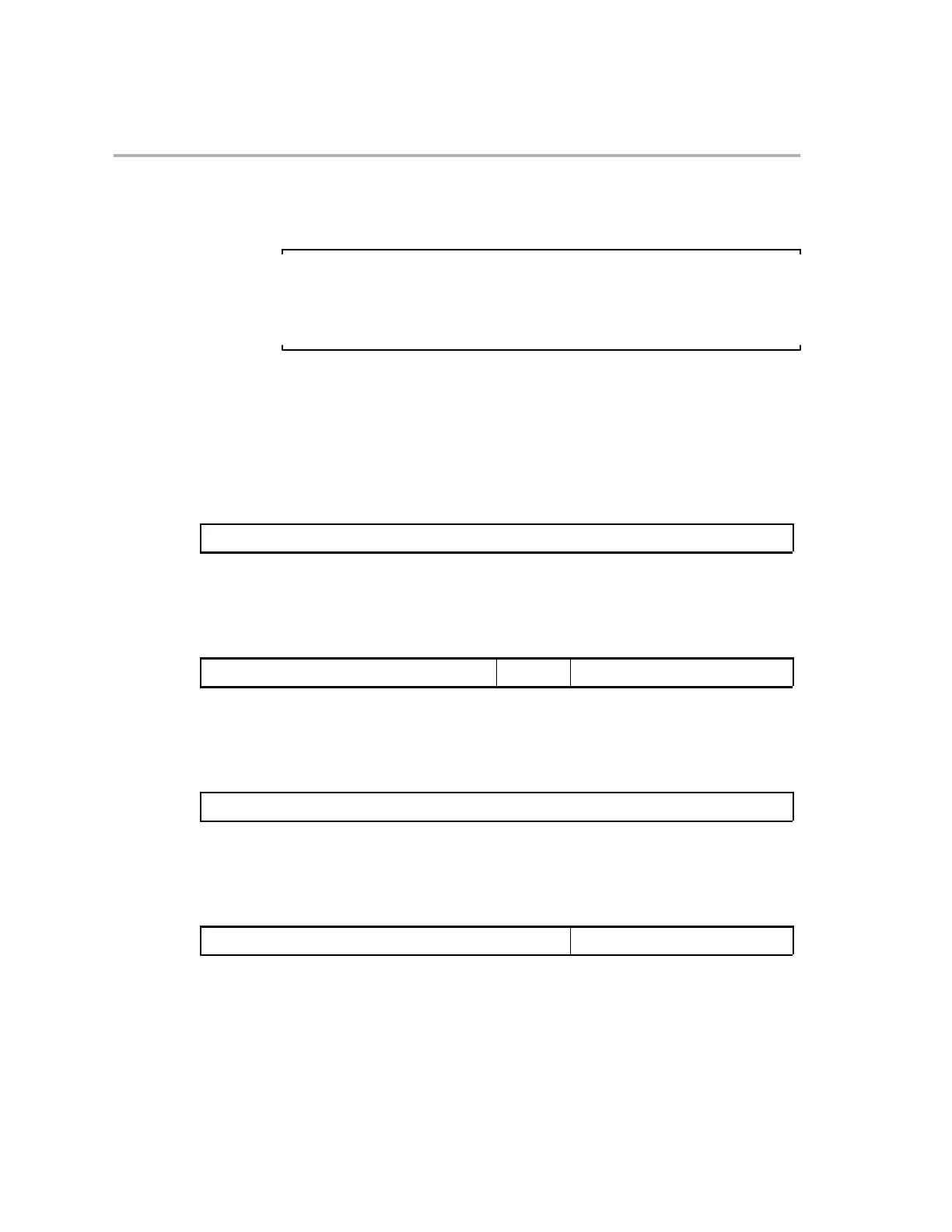

Figure 7−8. REFL (at Data-Space Address 00 084A

16

)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

16 LSBs of end address

Figure 7−9. REFH (at Data-Space Address 00 084B

16

)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0

0 0 0 0 0 0 0 0 0 6 MSBs of end address

Loading...

Loading...