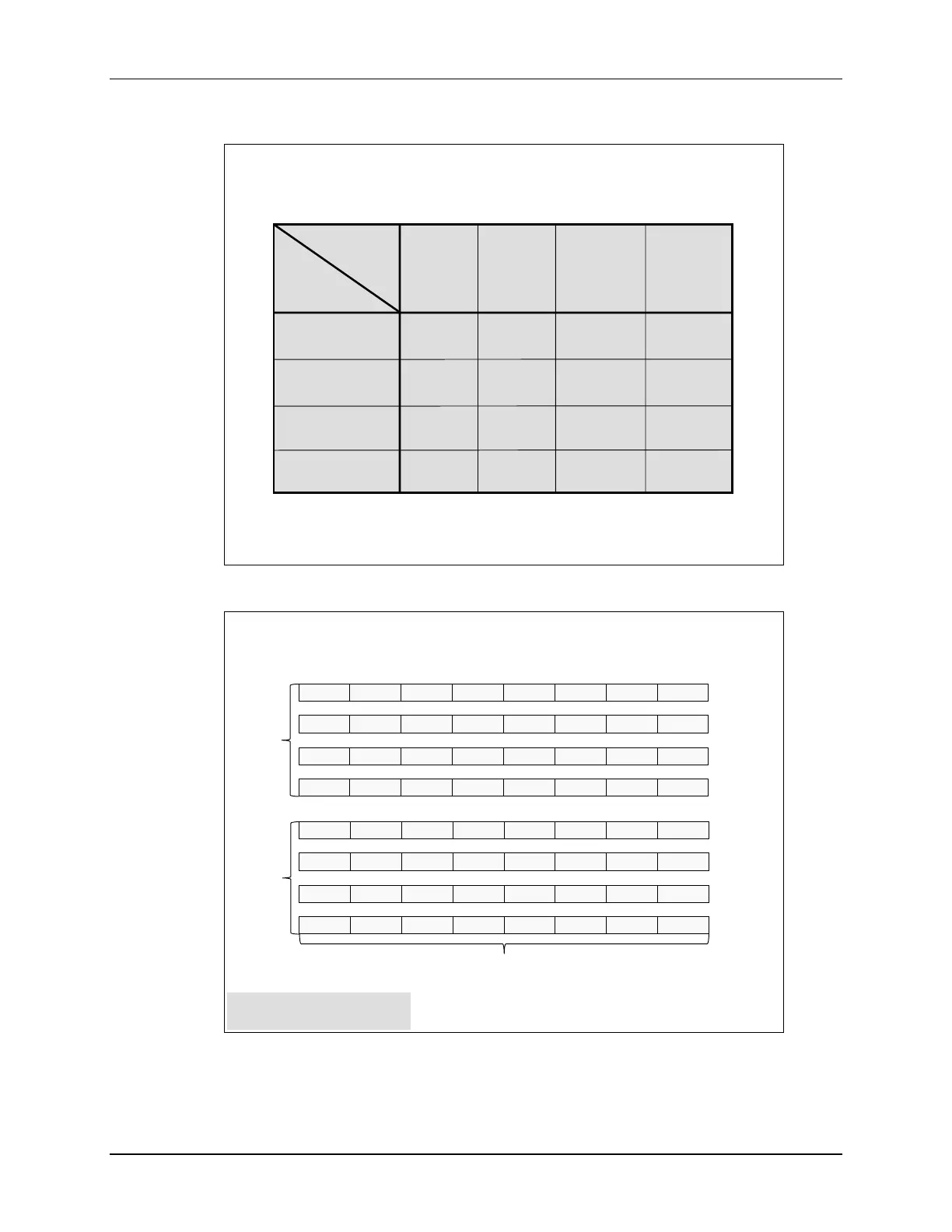

Low Power Mode Exit

IDLE

STANDBY

HALT

HIB

RESET

yes

yes

yes

yes

Any

Enabled

Interrupt

yes

no

no

no

yes

yes

no

no

Exit

Interrupt

Low Power

Mode

Watchdog

Interrupt

GPIO

Port A

Signal

yes

yes

yes

no*

* Hibernate - GPIO41 becomes HIBWAKE reset signal; boot ROM avoids

clearing M0 and M1 memories and calls a user-specified IO restore function

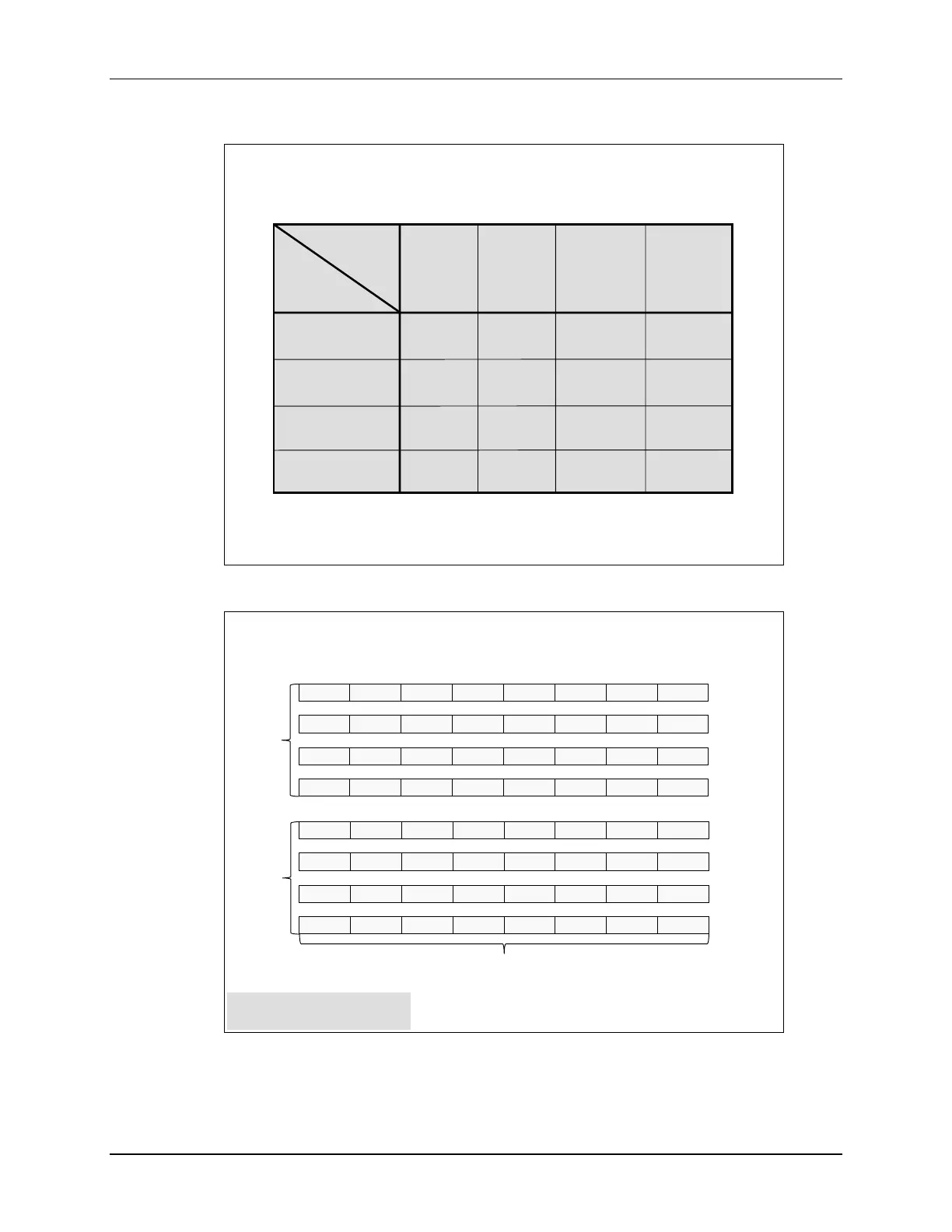

GPIO Low Power Wakeup Select

SysCtrlRegs.GPIOLPMSELx

Wake device from

STANDBY and HALT mode

(GPIO Port A & B)

0 = disable (default)

1 = enable

0

GPIO2GPIO5

1234567

GPIO0GPIO1GPIO4 GPIO3GPIO6GPIO7

GPIO14 GPIO8GPIO11

89101112131415

GPIO9GPIO10GPIO12GPIO13GPIO15

16

GPIO18GPIO21

17181920212223

GPIO16GPIO17GPIO20 GPIO19GPIO22GPIO23

GPIO30 GPIO24GPIO27

2425262728293031

GPIO25GPIO26GPIO28GPIO29GPIO31

0

GPIO34GPIO37

1234567

GPIO32GPIO33GPIO36 GPIO35GPIO38GPIO39

GPIO46 GPIO40GPIO43

89101112131415

GPIO41GPIO42GPIO44GPIO45GPIO47

16

GPIO50GPIO53

17181920212223

GPIO48GPIO49GPIO52 GPIO51GPIO54GPIO55

GPIO62

GPIO56

GPIO59

2425262728293031

GPIO57GPIO58GPIO60

GPIO61

GPIO63

x = 0

x = 1

Note: CPUSYSLOCK1 register can

be used to lock above registers

(lock bit for each register)

Loading...

Loading...