Control Law Accelerator (CLA)

TMS320F2837xD Microcontroller Workshop - Control Law Accelerator 9 - 3

Control Law Accelerator (CLA)

Control Law Accelerator (CLA)

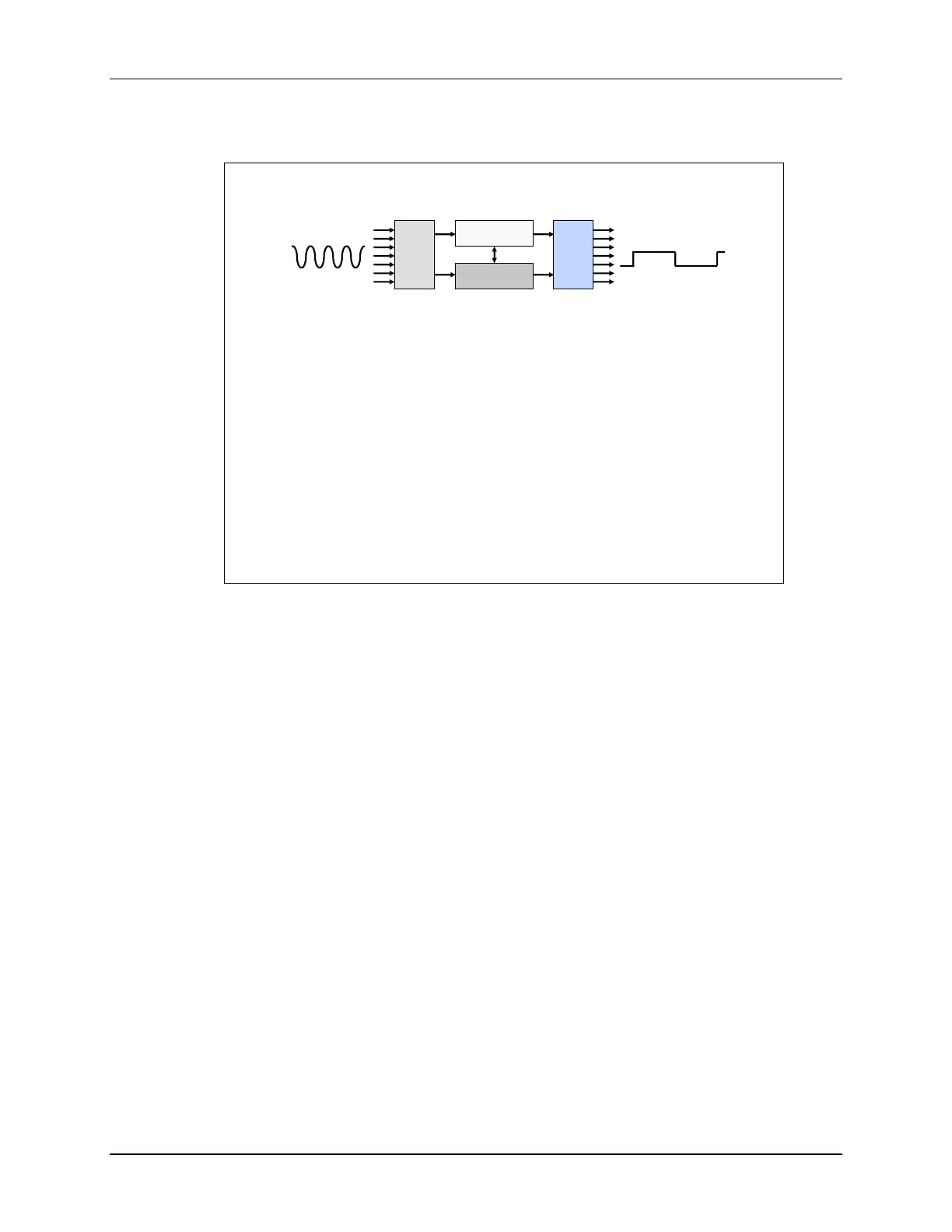

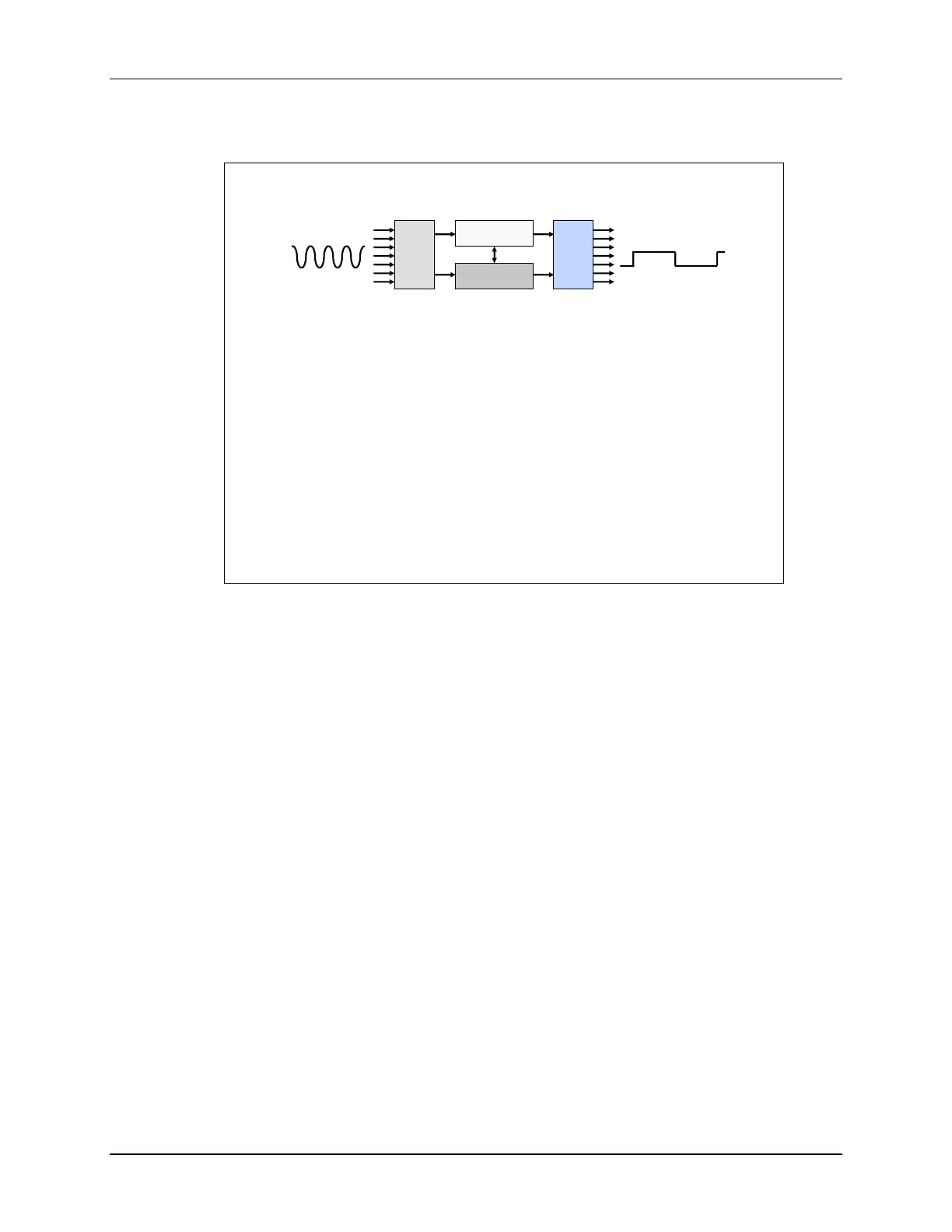

C28x CPU

CLA

PWM

ADC

&

CMP

The CLA is a 32-bit floating-point processor that responds

to peripheral triggers and executes code independent of

the main CPU

Designed for fast trigger response and oriented toward

math computations

Direct access to ePWM, HRPWM, eCAP, eQEP, ADC result,

CMPSS, DAC, SDFM, SPI, McBSP, GPIO and uPP registers

Frees up the CPU for other tasks (communications and

diagnostics)

The CLA is an independent 32-bit floating-point math hardware accelerator which executes real-

time control algorithms in parallel with the main C28x CPU, effectively doubling the computational

performance. Each CPU subsystem has its own CLA that responds directly to peripheral triggers,

which can free up the C28x CPU for other tasks, such as communications and diagnostics. With

direct access to the various control and communication peripherals, the CLA minimizes latency,

enables a fast trigger response, and avoids CPU overhead. Also, with direct access to the ADC

results registers, the CLA is able to read the result on the same cycle that the ADC sample

conversion is completed, providing “just-in-time” reading, which reduces the sample to output

delay.

Loading...

Loading...