External Memory Interface (EMIF)

Provides a means for the CPU, DMA, and CLA to connect

to various memory devices

Support for synchronous (SDRAM) and asynchronous

(SRAM, NOR Flash) memories

F2837xD includes two EMIFs

EMIF1 – 16/32-bit interface shared between CPU1 and CPU2

EMIF2 – 16-bit interface dedicated to CPU1

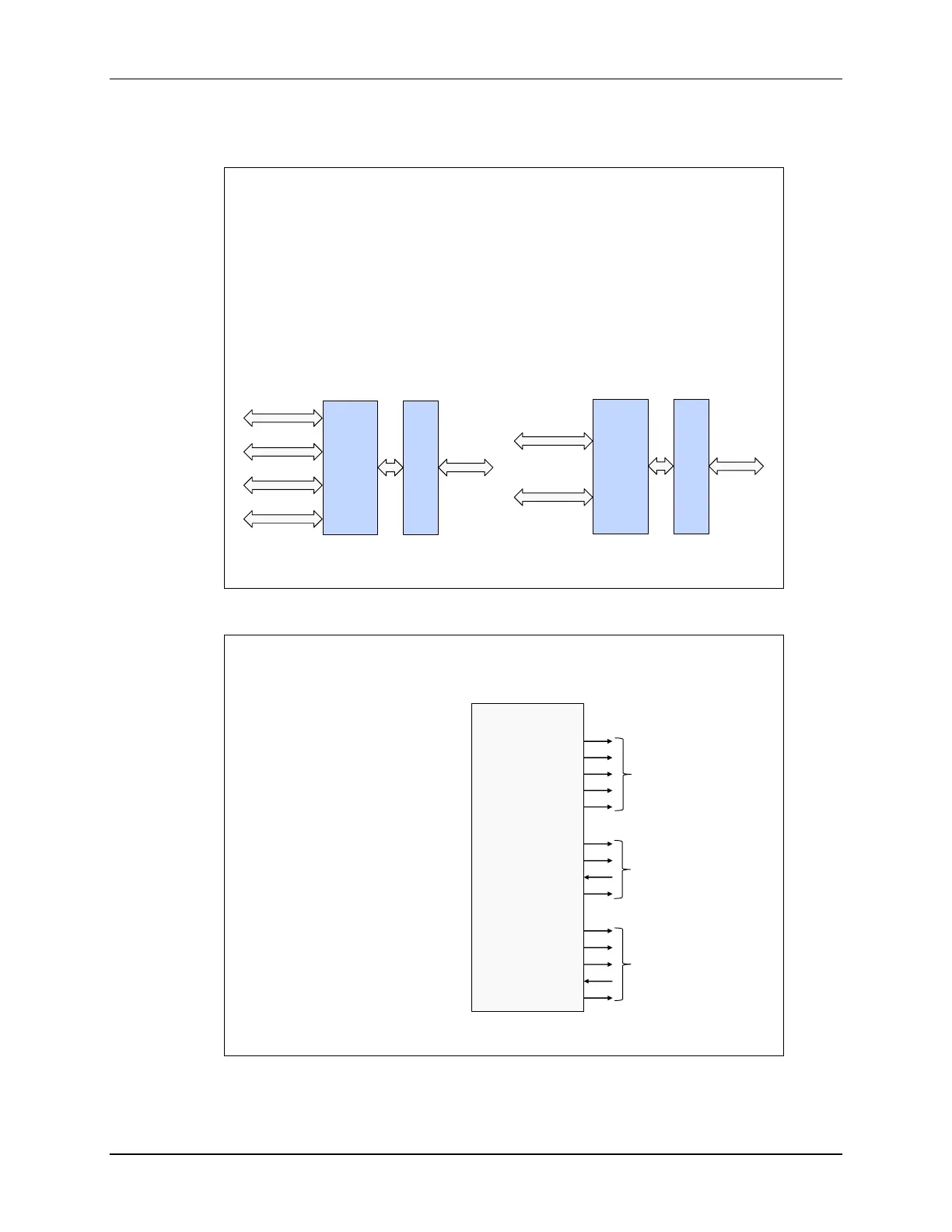

Arbiter/

Memory

Protection

EMIF1

16/32-Bit

Interface

CPU1

CPU1.DMA1

CPU2

CPU2.DMA1

Arbiter/

Memory

Protection

EMIF2

16-Bit

Interface

CPU1

CPU1.CLA1

EMIF1 shared between CPU1 & CPU2 EMIF2 dedicated to CPU1

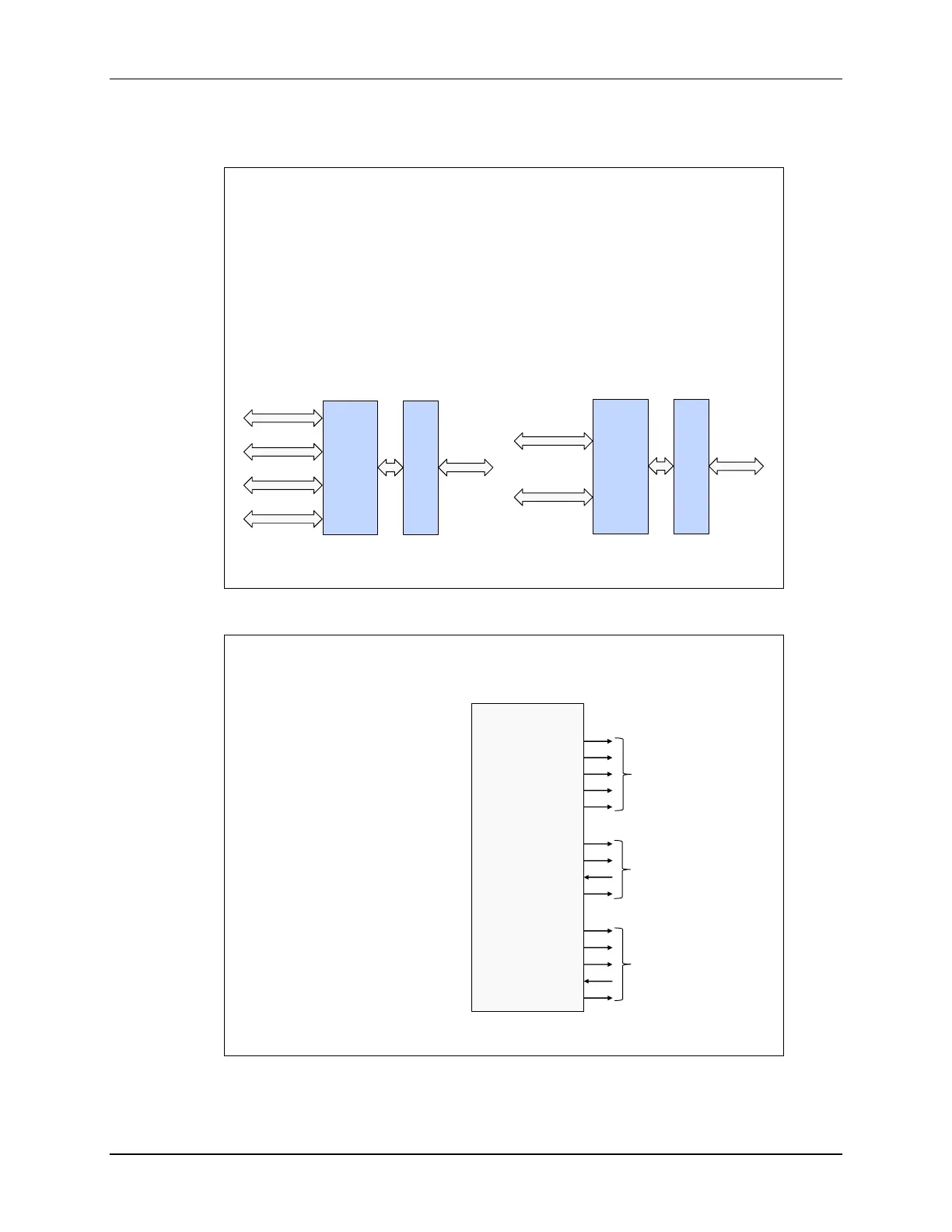

External Memory Interface Signals

EMIF_nCS[0]

EMIF_nCAS

EMIF_nRAS

EMIF_CLK

EMIF_CKE

EMIF_nCS[4:2]

EMIF_nOE

EMIF_WAIT

EMIF_RnW

EMIF_nWE

EMIF_BA[1:0]

EMIF_nDQM[x:0]

EMIF_D[x:0]

EMIF_A[x:0]

EMIF

SDRAM

Interface

Asynchronous

Interface

Shared SDRAM

and asynchronous

Interface

Chip select

Column address strobe

Row address strobe

SDRAM clock

Clock enable

Chip select pins

Output enable

Wait input with programmable polarity

Asynchronous read/write control

Write enable

Bank address pins

Byte enable pins

Data bus

Address bus

Loading...

Loading...