Interrupts

4 - 20 TMS320F2837xD Microcontroller Workshop - Reset and Interrupts

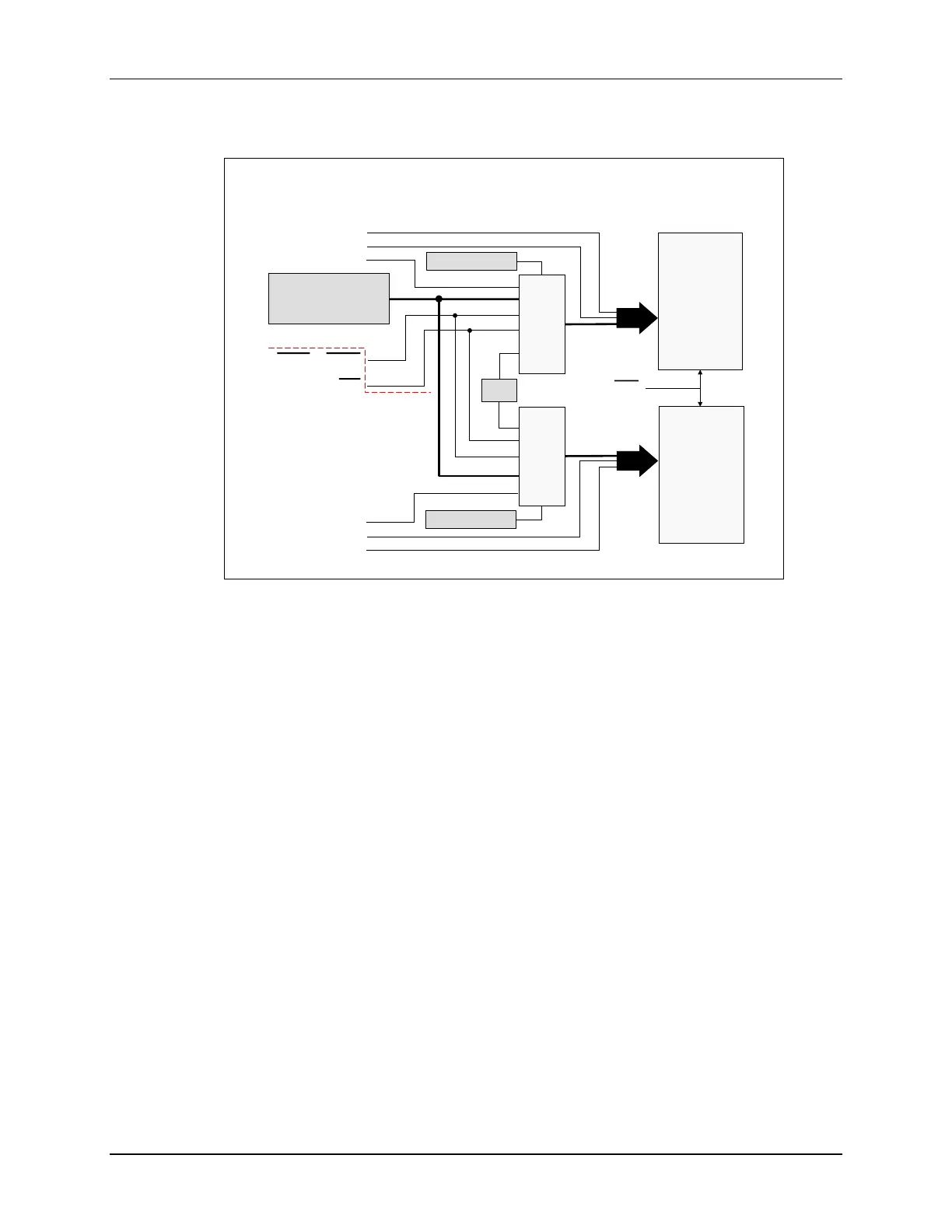

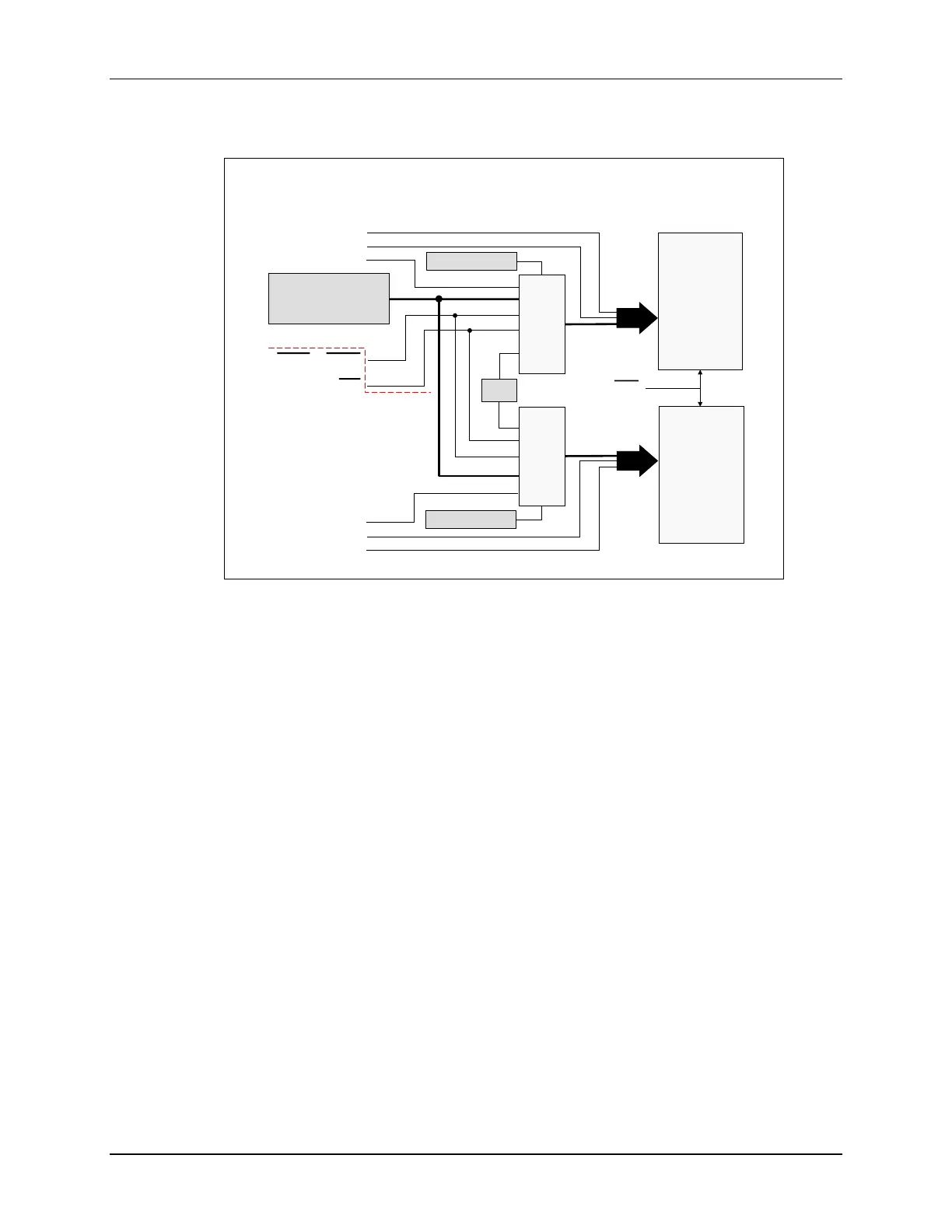

F2837xD Dual-Core Interrupt Structure

F2837xD Dual-Core Interrupt Structure

ePWM, eCAP, eQEP,

ADC, SCI, SPI, I2C,

CAN, McBSP, WD

Internal Sources

External Sources

TZx

XRS

NMI

CPU1 CORE

INT1

INT13

INT2

INT3

INT12

INT14

•

•

•

ePIE.1

TINT2.1

TINT1.1

TINT0.1

XINT1 – XINT5

DMA1.1 CLA1.1

TINT0.2

TINT1.2

TINT2.2

Internal Sources

NMI

CPU2 CORE

INT1

INT13

INT2

INT3

INT12

INT14

•

•

•

IPC

ePIE.2

DMA1.2 CLA1.2

Each C28x CPU core in the F2837xD device has its own PIE module, and each PIE module is

configured independently. Some interrupt signals are sourced from shared peripherals that can

be owned by either CPU, and these interrupt signals are sent to both CPU PIE modules

regardless of which CPU owns the peripheral. Therefore, if enabled a peripheral owned by one

CPU can cause an interrupt on the other CPU.

Loading...

Loading...