Math Accelerators

TMS320F2837xD Microcontroller Workshop - Architecture Overview 1 - 13

Math Accelerators

Viterbi / Complex Math Unit (VCU-II)

Viterbi / Complex Math Unit (VCU-II)

Extends C28x instruction

set to support:

Viterbi operations

Decode for communications

Complex math

16-bit fixed-point complex FFT

used in spread spectrum

communications, and many signal

processing algorithms

Complex filters

used to improve data reliability,

transmission distance, and power

efficiency

Power Line Communications

(PLC) and radar applications

Cyclic Redundancy Check

(CRC)

Communications and memory

robustness checks

Other: OFDM interleaving &

de-interleaving, Galois Field

arithmetic, AES acceleration

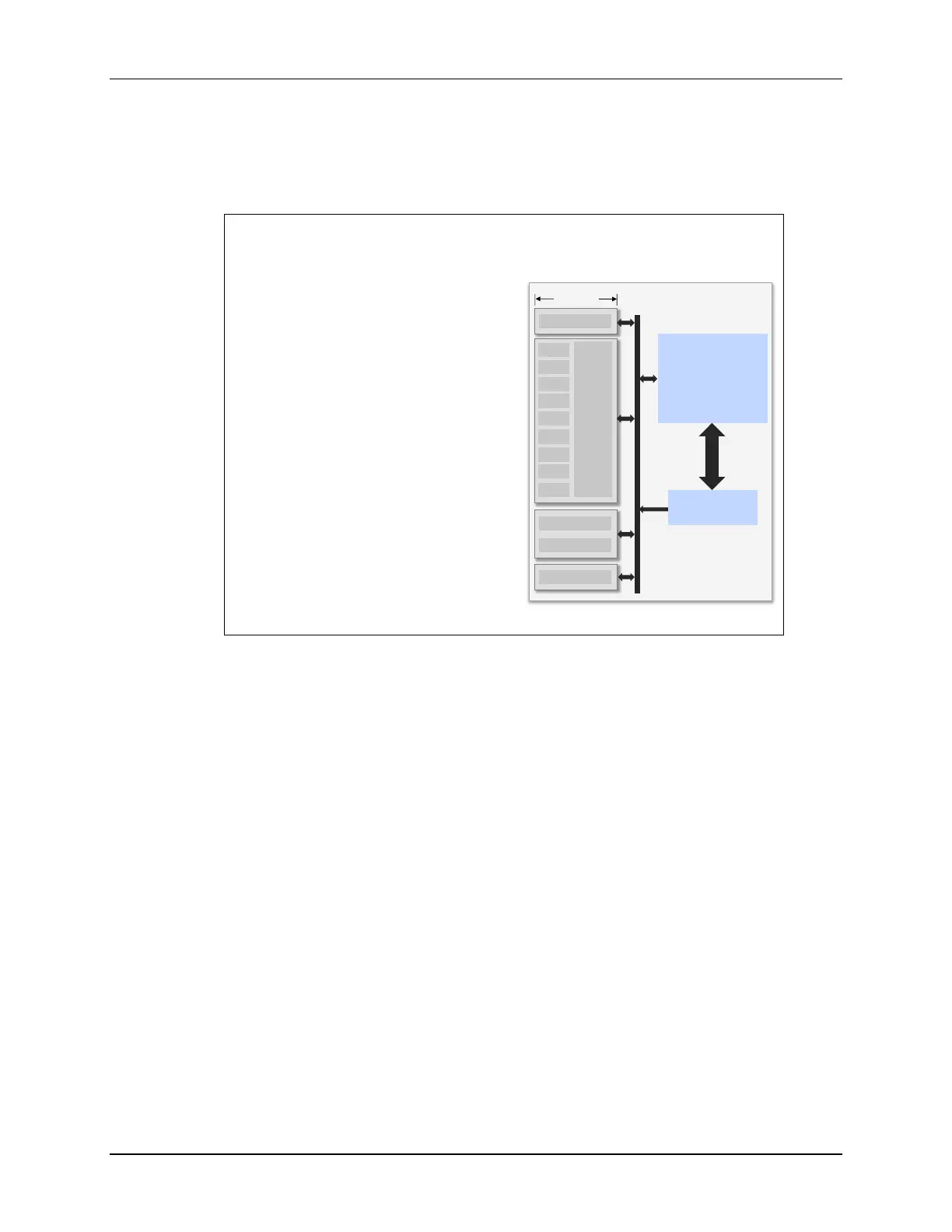

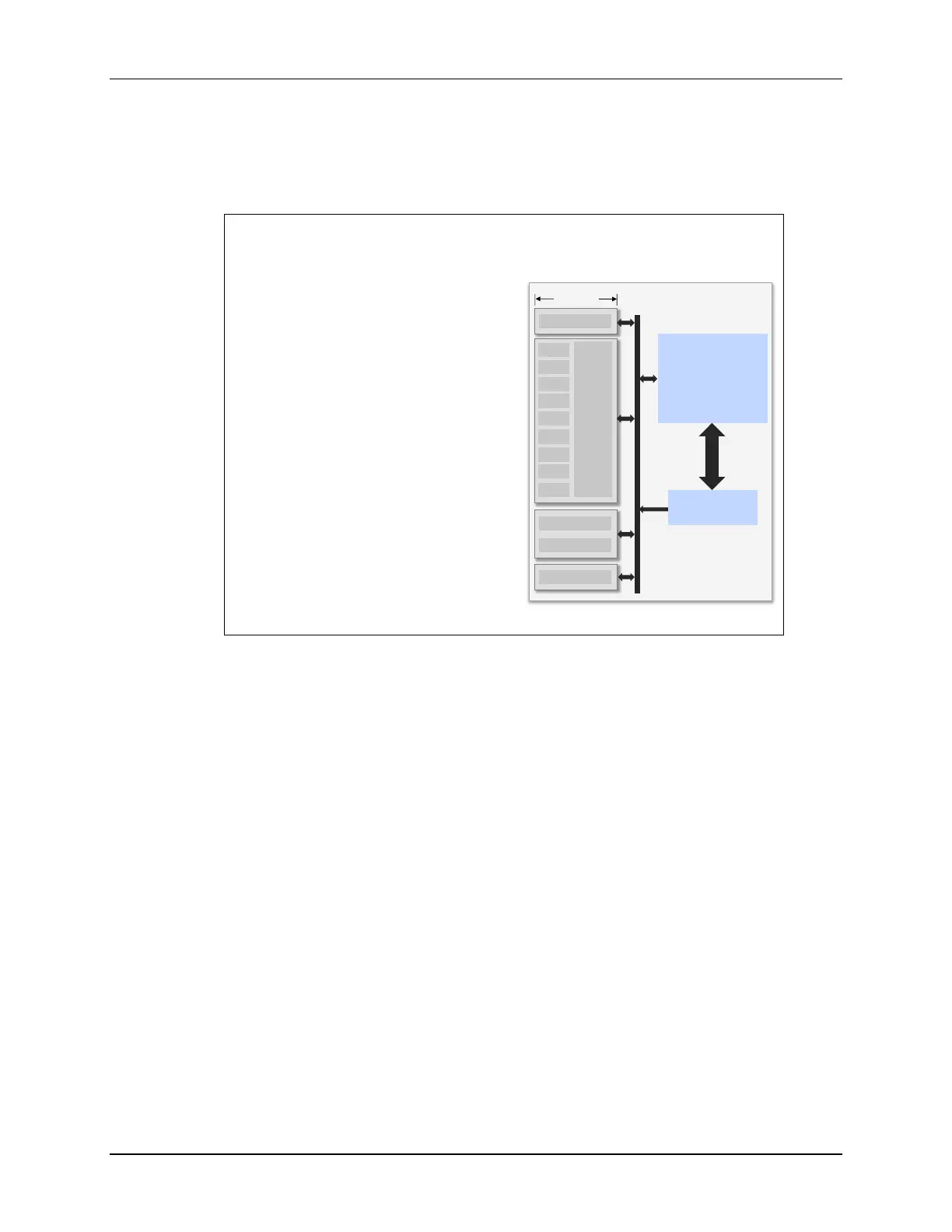

VCU execution

registers

VCU-II

VSTATUS

VR0

VR1

VR2

VR3

VR4

VR5

VR6

VR7

VR8

VT0

VT1

VCRC

VSM0

to

VSM63

Data path logic for VCU-II

Instruction

1. General instructions

2. CRC instructions

3. Arithmetic instructions

4. Galois Field instructions

5. Complex FFT instructions

VCU II

Control Logic

The Viterbi, Complex Math, and CRC Unit (VCU) adds an extended set of registers and

instructions to the standard C28x architecture for supporting various communications-based

algorithms, such as power line communications (PLC) standards PRIME and G3. These

algorithms typically require Viterbi decoding, complex Fast Fourier Transform (FFT), complex

filters, and cyclical redundancy check (CRC). By utilizing the VCU a significant performance

benefit is realized over a software implementation. It performs fixed-point operations using the

existing instruction set format, pipeline, and memory bus architecture. Additionally, the VCU is

very useful for general-purpose signal processing applications such as filtering and spectral

analysis.

Loading...

Loading...