Multichannel Buffered Serial Port (McBSP)

TMS320F2837xD Microcontroller Workshop - Communications 12 - 15

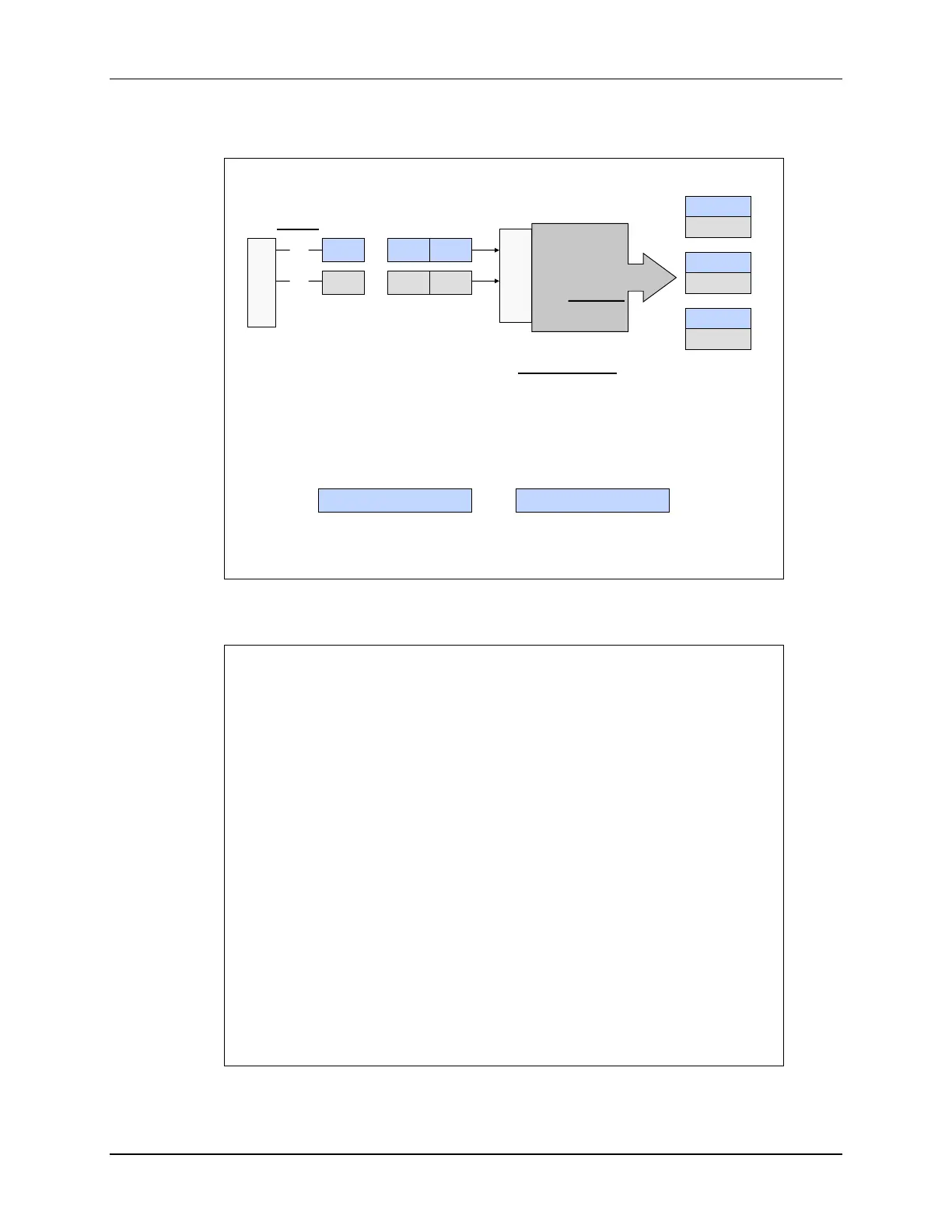

Multi-Channel Selection

Multi-Channel Selection

Ch0-0

Ch0-1

Ch5-0

Ch5-1

Ch27-0

Ch27-1

Multi-channel mode controlled primarily via two registers:

MCR

Multi-channel Control Reg

(enables Mc-mode)

R/XCER (A-H)

Rec/Xmt Channel Enable Regs

(enable/disable channels)

Up to 128 channels can be enabled/disabled

C

O

D

E

C

M

c

B

S

P

Frame TDM Bit Stream

Ch0Ch1

Ch31

...

0

Ch0Ch1Ch31

...

1

Transmit

&

Receive

only selected

Channels

Multi-channel

Allows multiple channels (words) to be independently selected for transmit

and receive (e.g. only enable Ch0, 5, 27 for receive, then process via CPU)

The McBSP keeps time sync with all channels, but only “listens” or “talks”

if the specific channel is enabled (reduces processing/bus overhead)

McBSP Summary

McBSP Summary

Independent clocking and framing for

transmit and receive

Internal or external clock and frame sync

Data size of 8, 12, 16, 20, 24, or 32 bits

TDM mode - up to 128 channels

Used for T1/E1 interfacing

m-law and A-law companding

SPI mode

Direct Interface to many codecs

Can be serviced by the DMA

Loading...

Loading...