Interrupts

TMS320F2837xD Microcontroller Workshop - Reset and Interrupts 4 - 13

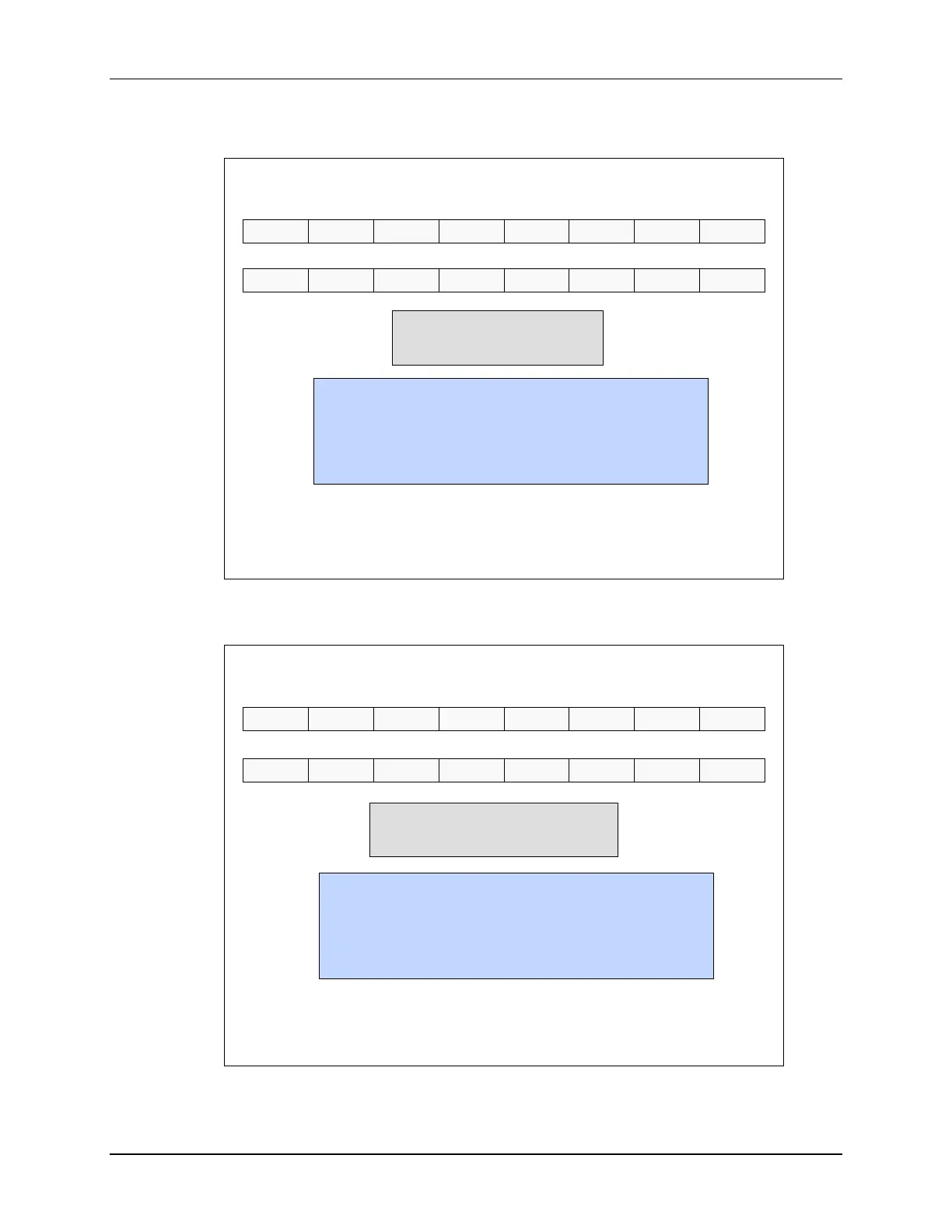

Interrupt Flag Register (IFR)

Interrupt Flag Register (IFR)

RTOSINT DLOGINT INT14 INT13 INT12 INT11

INT10

INT9

8

9

10

11

121314

15

INT8 INT7 INT6 INT5 INT4 INT3 INT2

INT1

0

1

2

3

456

7

Pending : IFR

Bit

= 1

Absent : IFR

Bit

= 0

Compiler generates atomic instructions (non-interruptible) for setting/clearing IFR

If interrupt occurs when writing IFR, interrupt has priority

IFR(bit) cleared when interrupt is acknowledged by CPU

Register cleared on reset

/*** Manual setting/clearing IFR ***/

extern cregister volatile unsigned int IFR;

IFR |= 0x0008; //set INT4 in IFR

IFR &= 0xFFF7; //clear INT4 in IFR

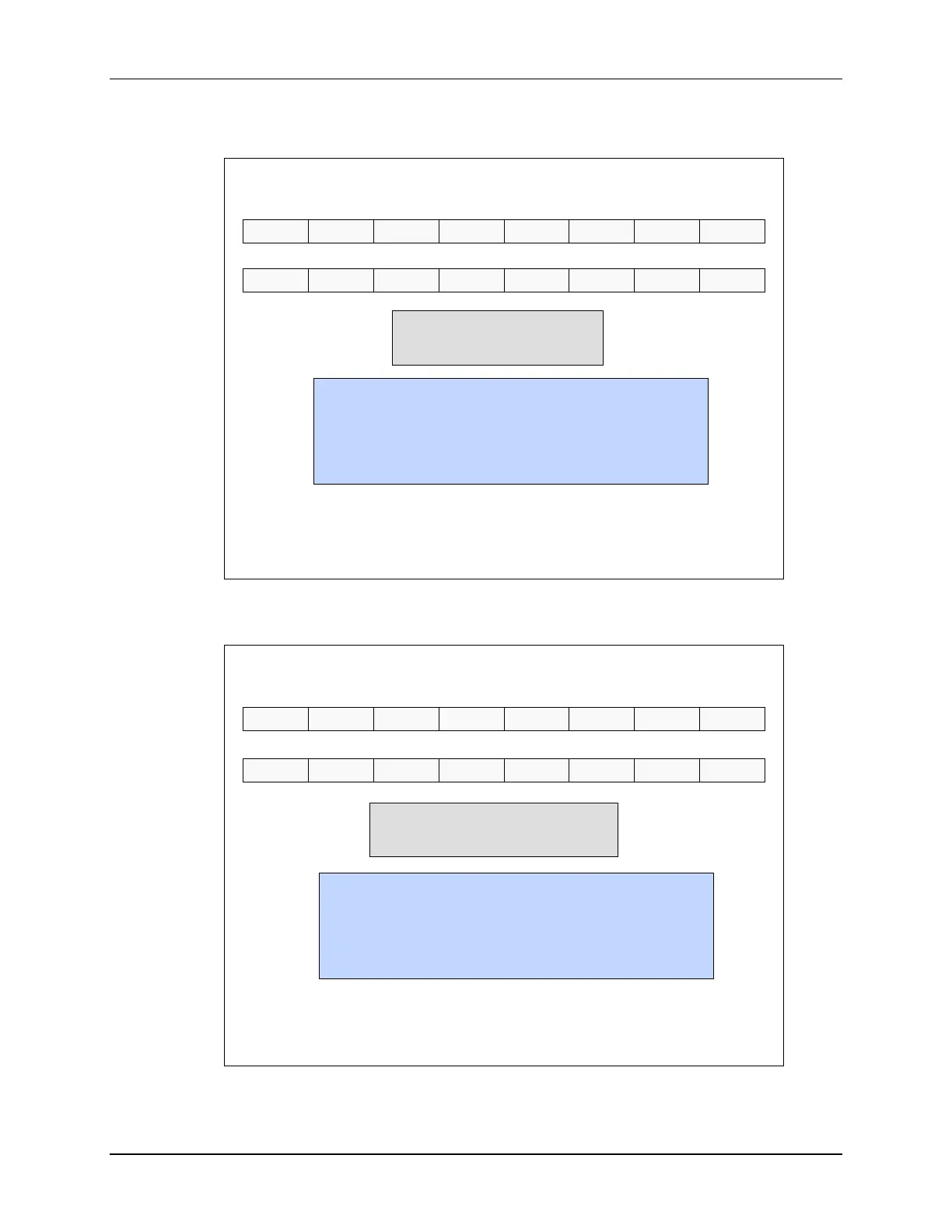

Interrupt Enable Register (IER)

Interrupt Enable Register (IER)

RTOSINT DLOGINT INT14 INT13 INT12 INT11 INT10 INT9

8

9

10

11

121314

15

INT8 INT7 INT6 INT5 INT4 INT3 INT2 INT1

0

1

2

3

456

7

Enable: Set IER

Bit

= 1

Disable: Clear IER

Bit

= 0

Compiler generates atomic instructions (non-interruptible)

for setting/clearing IER

Register cleared on reset

/*** Interrupt Enable Register ***/

extern cregister volatile unsigned int IER;

IER |= 0x0008; //enable INT4 in IER

IER &= 0xFFF7; //disable INT4 in IER

Loading...

Loading...