Control Law Accelerator (CLA)

9 - 6 TMS320F2837xD Microcontroller Workshop - Control Law Accelerator

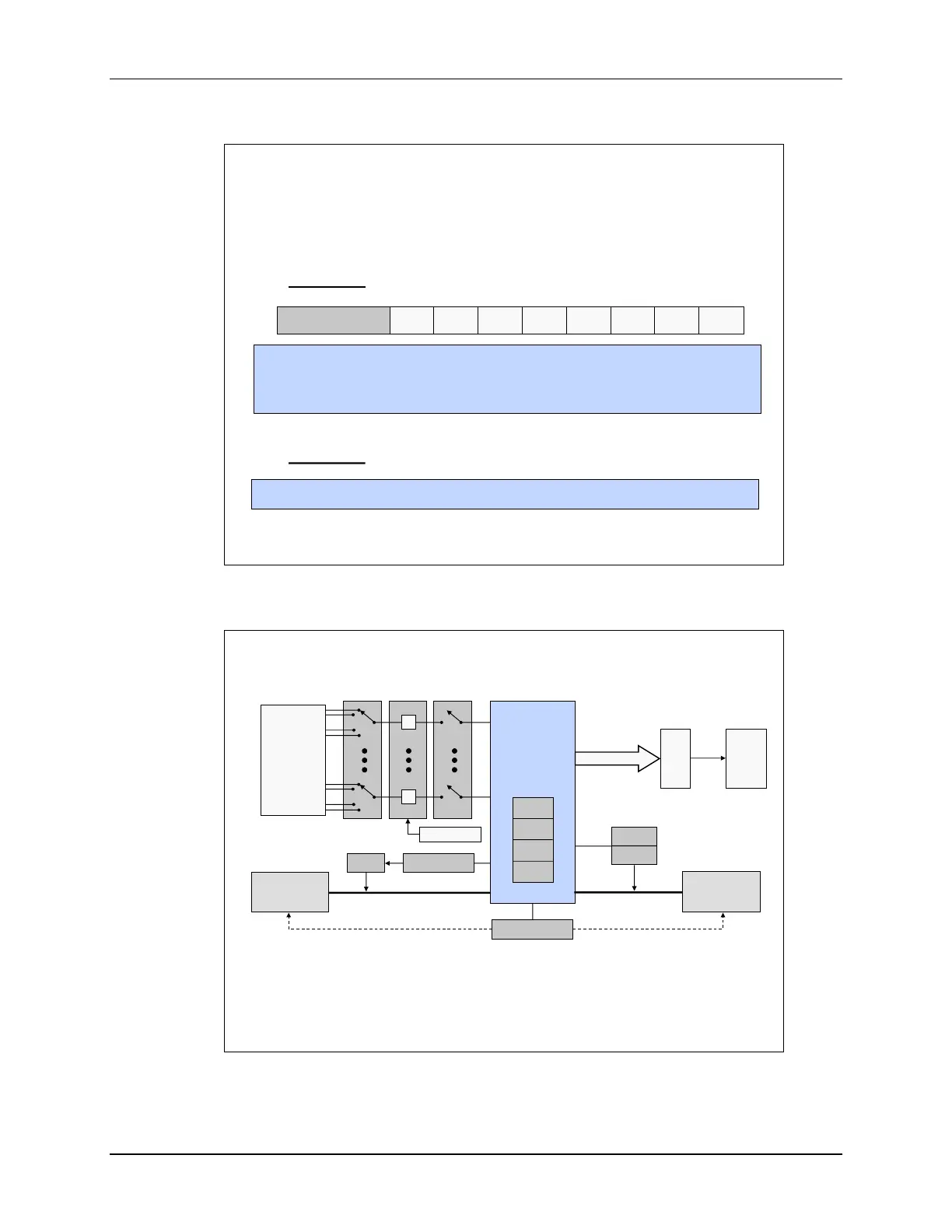

Software Triggering a Task

Tasks can also be started by a software trigger

using the CPU

asm(" EALLOW"); //enable protected register access

Cla1Regs.MIFRC.bit.INT4 = 1; //start task 4

asm(" EDIS"); //disable protected register access

Method #1: Write to Interrupt Force Register (MIFRC) register

INT2INT3INT4INT5INT6INT7INT8 INT1

0123456715 - 8

reserved

Method #2: Use IACK instruction

asm(" IACK #0x0008"); //set bit 3 in MIFRC to start task 4

More efficient – does not require EALLOW

Note: Use of IACK requires Cla1Regs.MCTL.bit.IACKE = 1

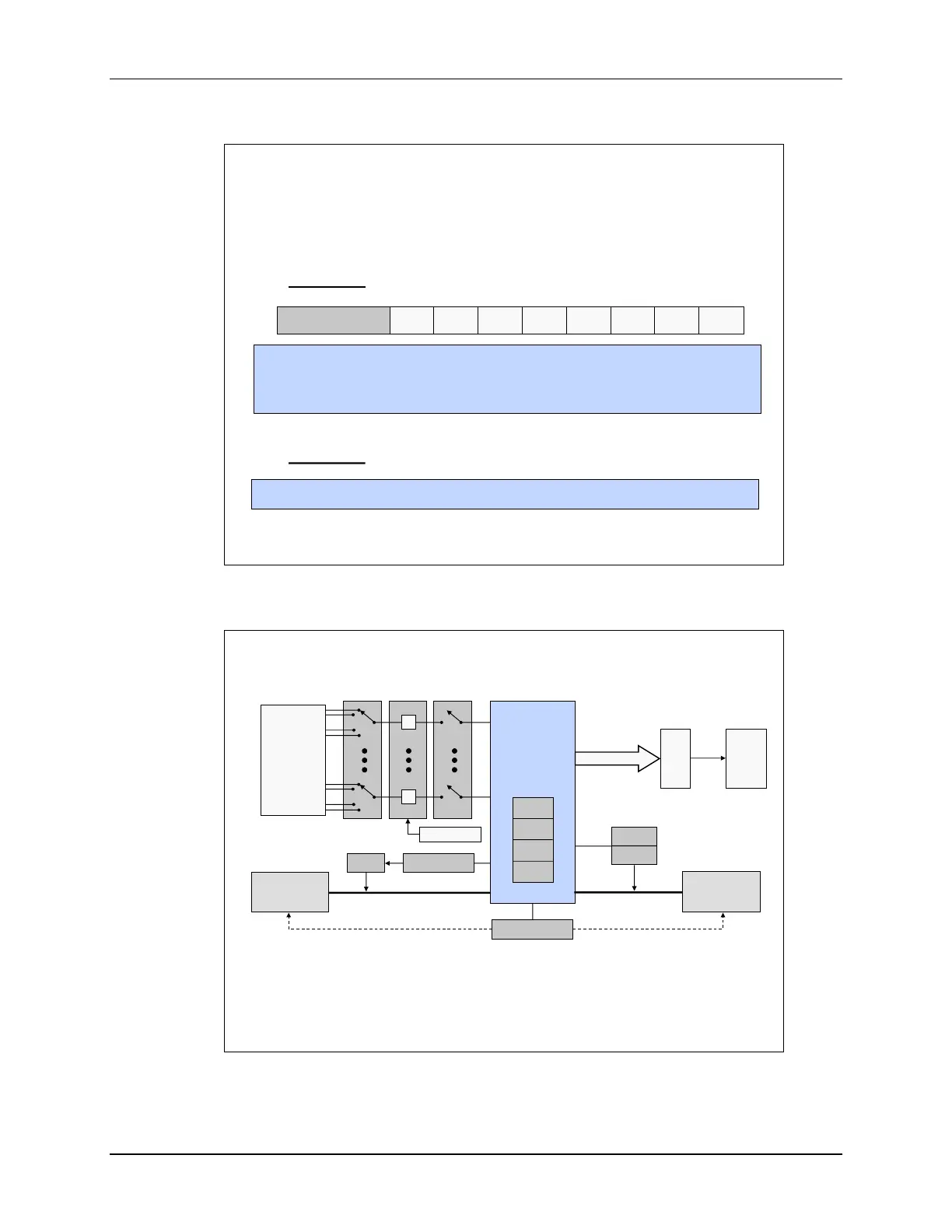

CLA Control and Execution Registers

CLA Control and Execution Registers

CLA1TASKSRCSELx – Task Interrupt Source Select (Task 1-8)

MVECT1-8 – Task Interrupt Vector (MVECT1/2/3/4/5/6/7/8)

LSxCLAPGM – Memory Map Configuration (LS0 – LS5 RAM)

MPC – 16-bit Program Counter (initialized by appropriate MVECTx register)

MR0-3 – CLA Floating-Point Result Registers (32 bit)

MAR0-1 – CLA Auxiliary Registers (16 bit)

1

0

MIFR

MIER

CLA1TASKSRCSELx

CLA

Core

CLA Program Bus

CLA Data Bus

Program

Memory

Data

Memory

LSxCLAPGM

MVECT1-8

MPC

MAR0

MAR1

CLA_INT1-8

LVF, LUF

MR0

MR1

MR2

MR3

PIE

C28x

CPU

INT11

INT12

S/W Trigger

MIFRC

Task

Source

Triggers

•

•

•

•

•

•

•

•

•

•

•

•

Loading...

Loading...