Serial Peripheral Interface (SPI)

12 - 4 TMS320F2837xD Microcontroller Workshop - Communications

Serial Peripheral Interface (SPI)

The SPI is a high-speed synchronous serial port that shifts a programmable length serial bit

stream into and out of the device at a programmable bit-transfer rate. It is typically used for

communications between processors and external peripherals, and it has a 16-level deep receive

and transmit FIFO for reducing servicing overhead. During data transfers, one SPI device must

be configured as the transfer MASTER, and all other devices configured as SLAVES. The

master drives the transfer clock signal for all SLAVES on the bus. SPI communications can be

implemented in any of three different modes:

• MASTER sends data, SLAVES send dummy data

• MASTER sends data, one SLAVE sends data

• MASTER sends dummy data, one SLAVE sends data

In its simplest form, the SPI can be thought of as a programmable shift register. Data is shifted in

and out of the SPI through the SPIDAT register. Data to be transmitted is written directly to the

SPIDAT register, and received data is latched into the SPIBUF register for reading by the CPU.

This allows for double-buffered receive operation, in that the CPU need not read the current

received data from SPIBUF before a new receive operation can be started. However, the CPU

must read SPIBUF before the new operation is complete of a receiver overrun error will occur. In

addition, double-buffered transmit is not supported: the current transmission must be complete

before the next data character is written to SPIDAT or the current transmission will be corrupted.

The Master can initiate a data transfer at any time because it controls the SPICLK signal. The

software, however, determines how the Master detects when the Slave is ready to broadcast.

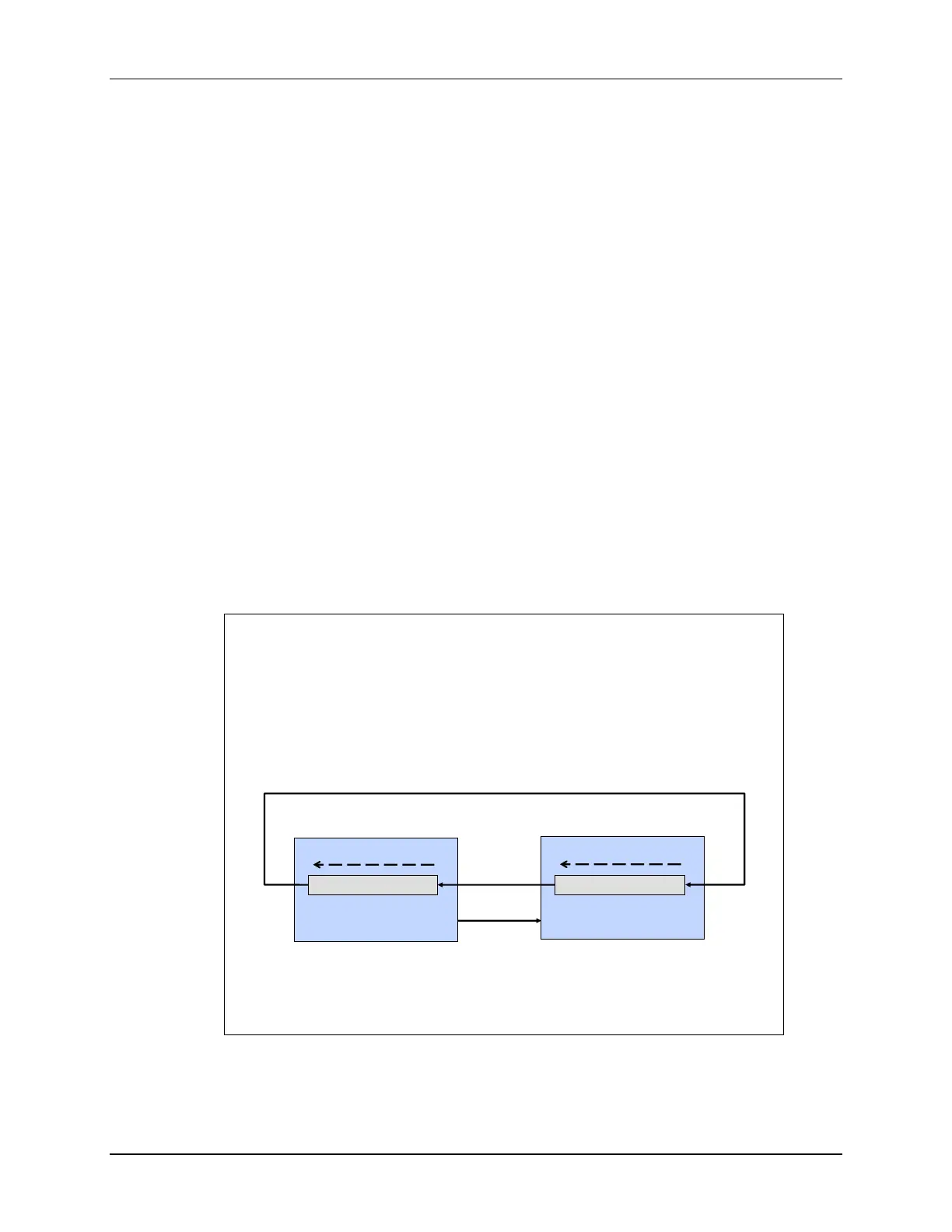

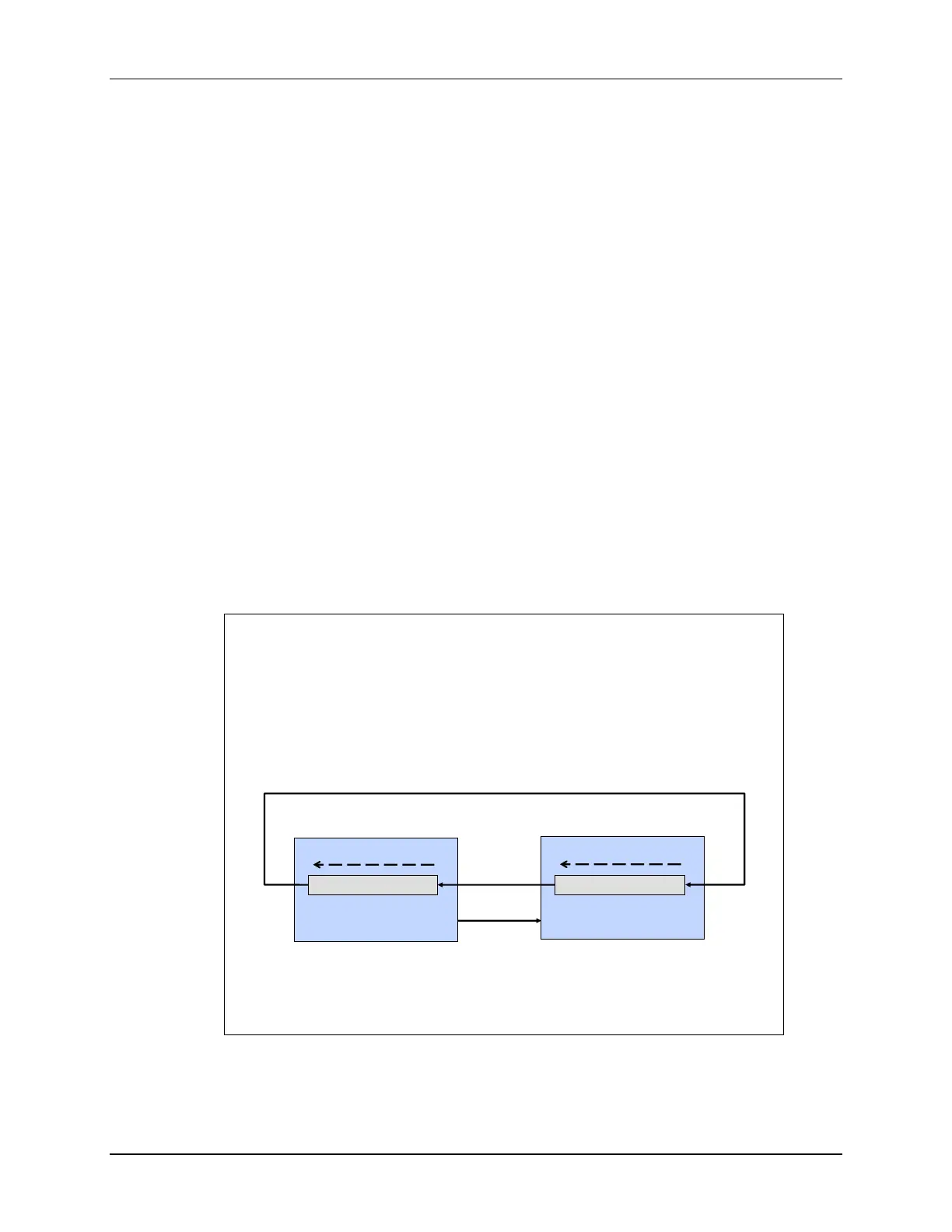

SPI Data Flow

Simultaneous transmits and receive

SPI Master provides the clock signal

SPI Shift Register

SPI Device #1 - Master SPI Device #2 - Slave

shift

shift

clock

SPI Shift Register

Loading...

Loading...