Serial Peripheral Interface (SPI)

TMS320F2837xD Microcontroller Workshop - Communications 12 - 5

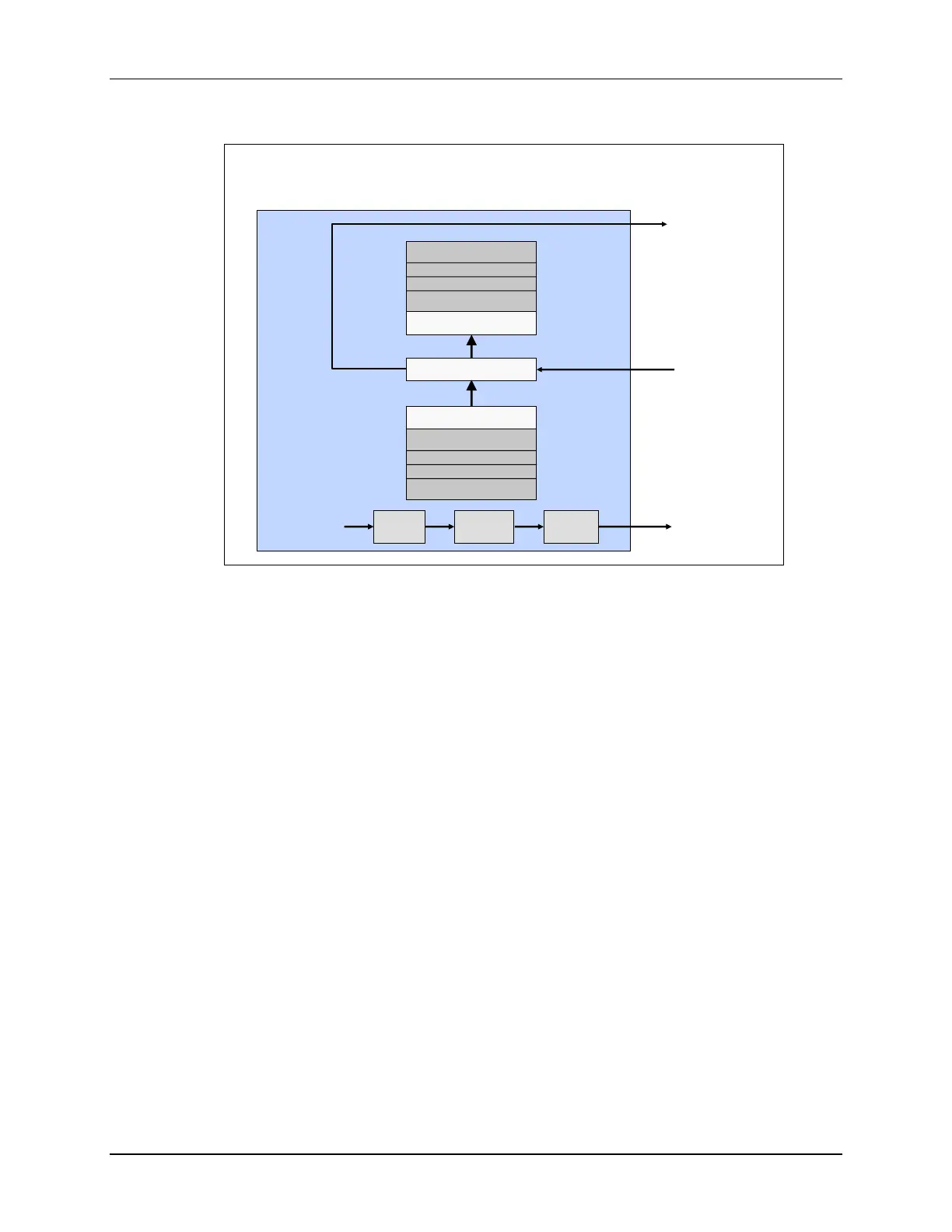

SPI Block Diagram

SPIRXBUF.15-0

SPIDAT.15-0

SPICLK

SPISOMI

SPISIMO

LSPCLK

baud

rate

clock

polarity

clock

phase

C28x - SPI Master Mode Shown

SPITXBUF.15-0

LSB

MSB

TX FIFO_0

TX FIFO_3

RX FIFO_0

RX FIFO_3

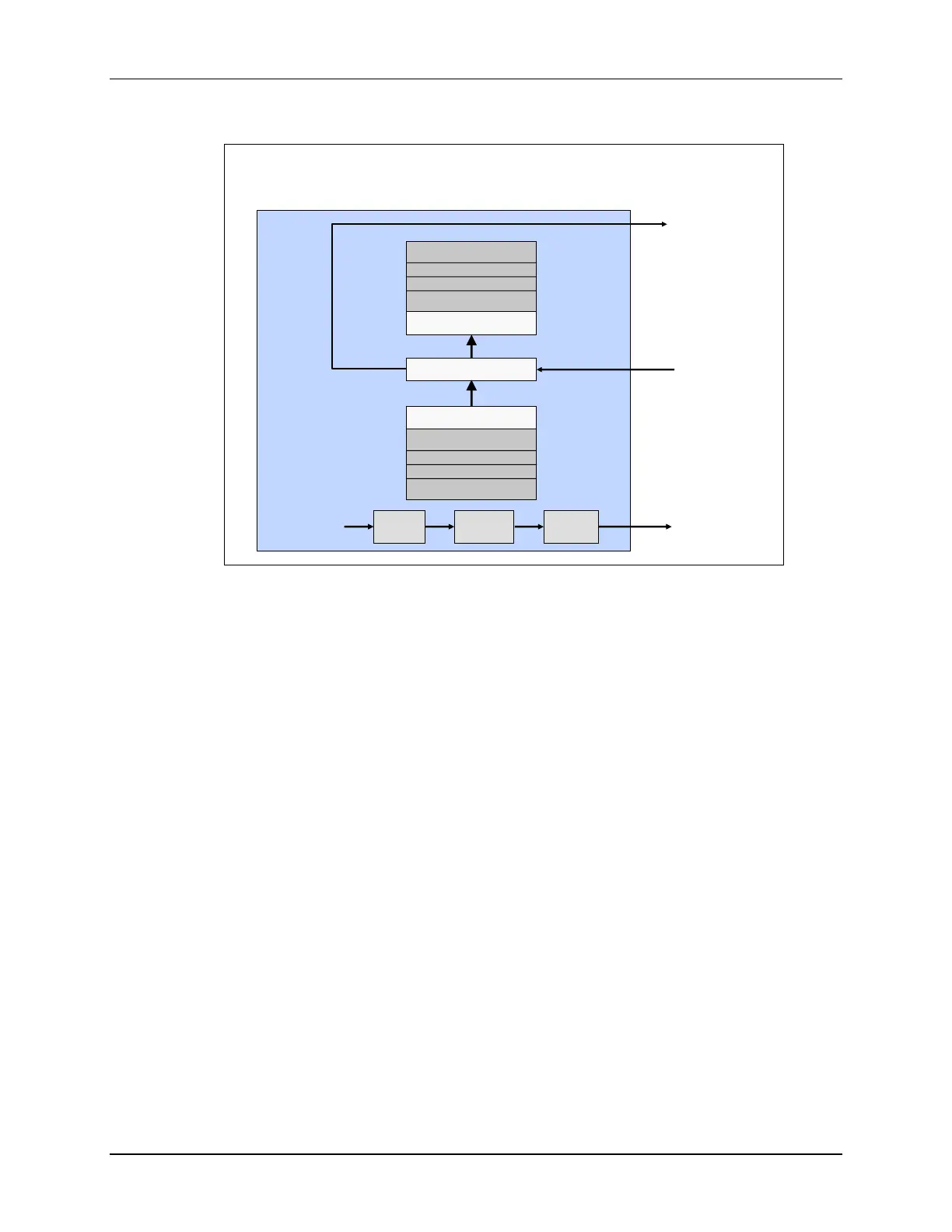

SPI Transmit / Receive Sequence

1. Slave writes data to be sent to its shift register (SPIDAT)

2. Master writes data to be sent to its shift register (SPIDAT or SPITXBUF)

3. Completing Step 2 automatically starts SPICLK signal of the Master

4. MSB of the Master’s shift register (SPIDAT) is shifted out, and LSB of the Slave’s shift

register (SPIDAT) is loaded

5. Step 4 is repeated until specified number of bits are transmitted

6. SPIDAT register is copied to SPIRXBUF register

7. SPI INT Flag bit is set to 1

8. An interrupt is asserted if SPI INT ENA bit is set to 1

9. If data is in SPITXBUF (either Slave or Master), it is loaded into SPIDAT and transmission

starts again as soon as the Master’s SPIDAT is loaded

Loading...

Loading...