C28x CPU + FPU + VCU + TMU and CLA

TMS320F2837xD Microcontroller Workshop - Architecture Overview 1 - 7

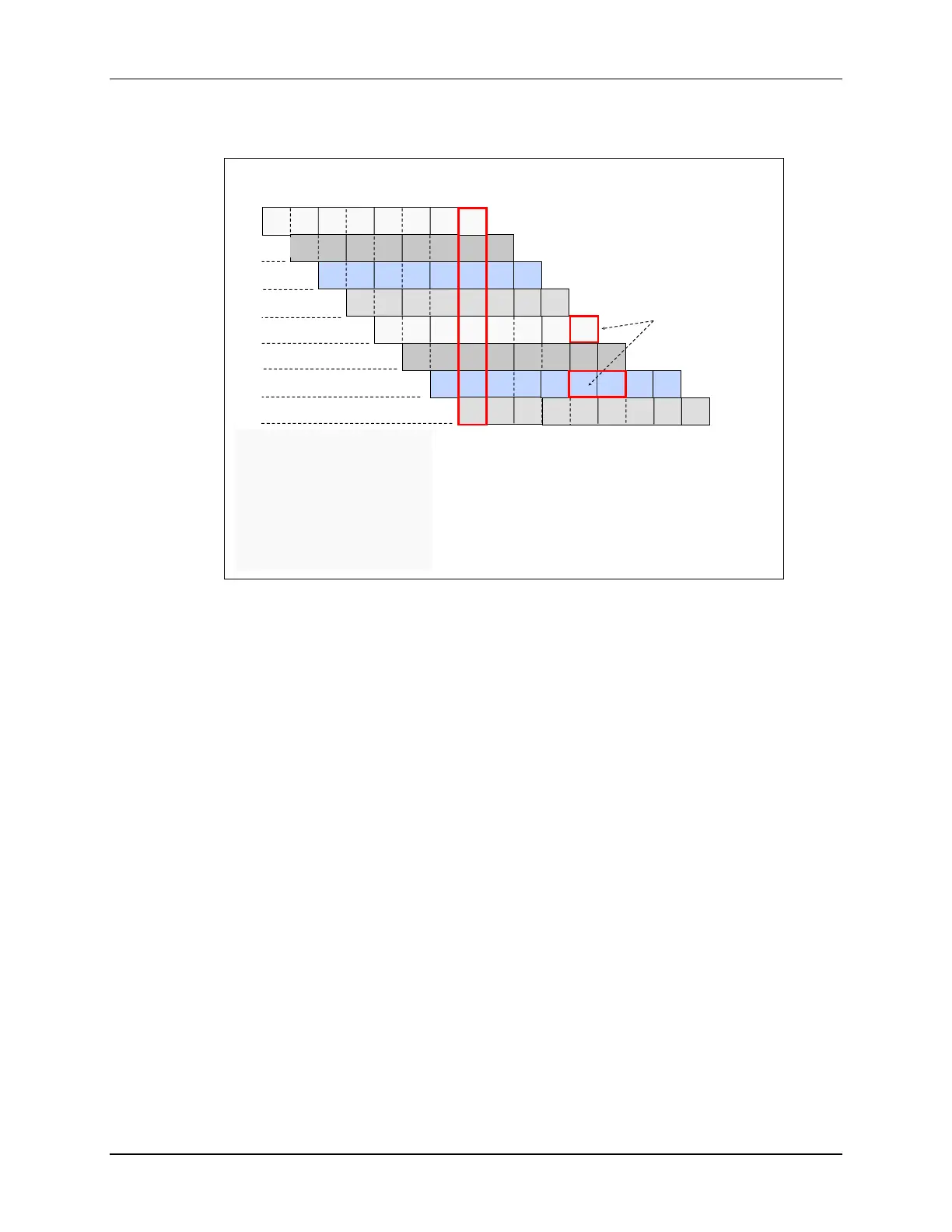

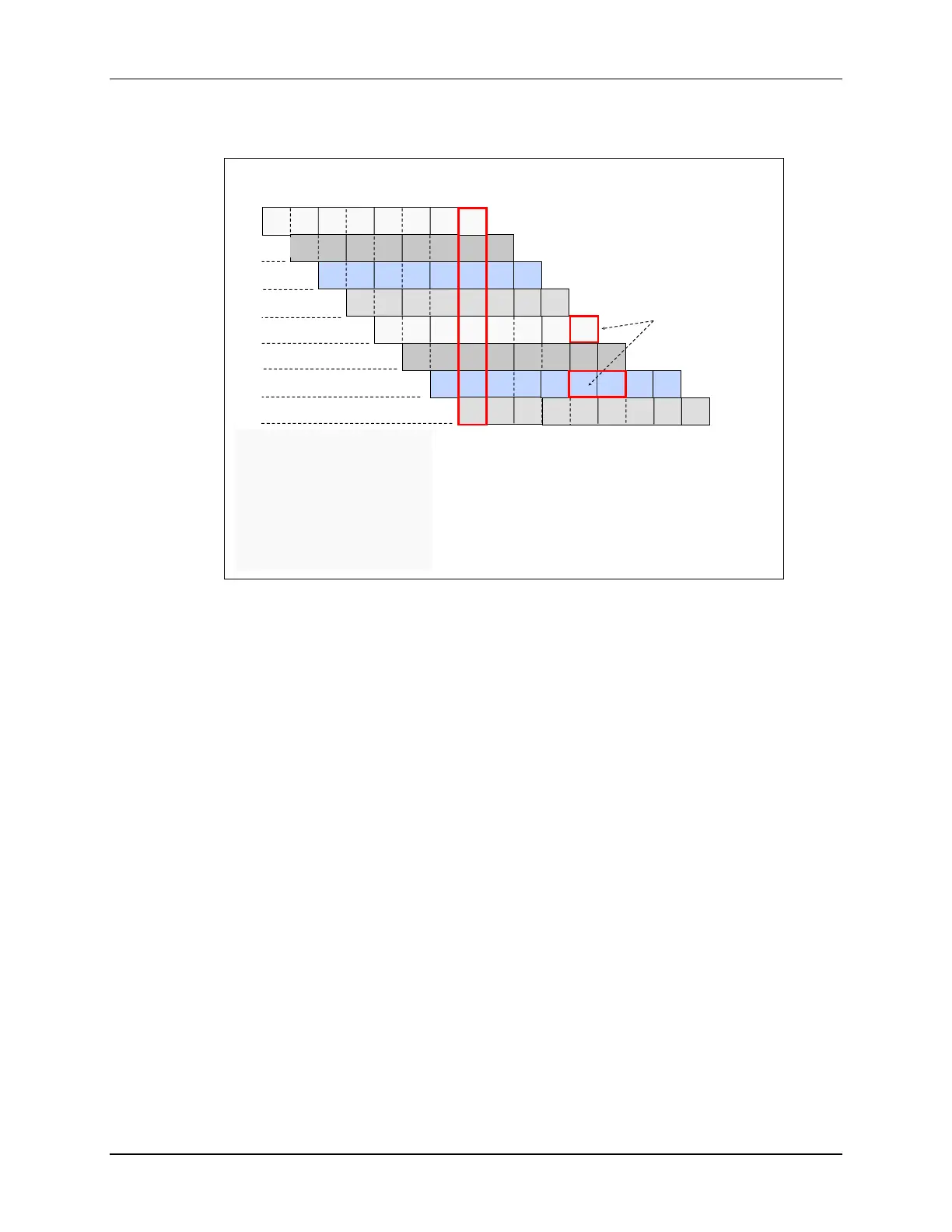

CPU Pipeline

F

1

F

2

D

1

D

2

R

1

R

2

E

C28x CPU Pipeline

Protected Pipeline

Order of results are as written in

source code

Programmer need not worry about

the pipeline

8-stage pipeline

F

1

F

2

D

1

D

2

R

1

R

2

E

F

1

F

2

D

1

D

2

R

1

R

2

E

F

1

F

2

D

1

D

2

R

1

R

2

E

F

1

F

2

D

1

D

2

R

1

R

2

E

F

1

F

2

D

1

D

2

R

1

R

2

E

F

1

F

2

D

1

D

2

R

1

R

2

E

F

1

F

2

D

1

D

2

R

1

R

2

E

A

B

C

D

E

F

G

W

W

W

W

W

W

W

W

E & G Access

same address

R

1

R

2

E W

D

2

R

1

R

2

E W

F1: Instruction Address

F2: Instruction Content

D1: Decode Instruction

D2: Resolve Operand Addr

R1: Operand Address

R2: Get Operand

E: CPU doing “real” work

W: store content to memory

H

The C28x uses a special 8-stage protected pipeline to maximize the throughput. This protected

pipeline prevents a write to and a read from the same location from occurring out of order.

This pipelining also enables the C28x CPU to execute at high speeds without resorting to

expensive high-speed memories. Special branch-look-ahead hardware minimizes the latency for

conditional discontinuities. Special store conditional operations further improve performance.

With the 8-stage pipeline most operations can be performed in a single cycle.

Loading...

Loading...