Inter-Processor Communications

TMS320F2837xD Microcontroller Workshop - Dual-Core Inter-Processor Communications 11 - 3

Inter-Processor Communications

IPC Features

Message RAMs

IPC flags and interrupts

IPC command registers

Flash pump semaphore

Clock configuration semaphore

Free-running counter

Allows Communications Between the

Two CPU Subsystems

All IPC features are independent of each other

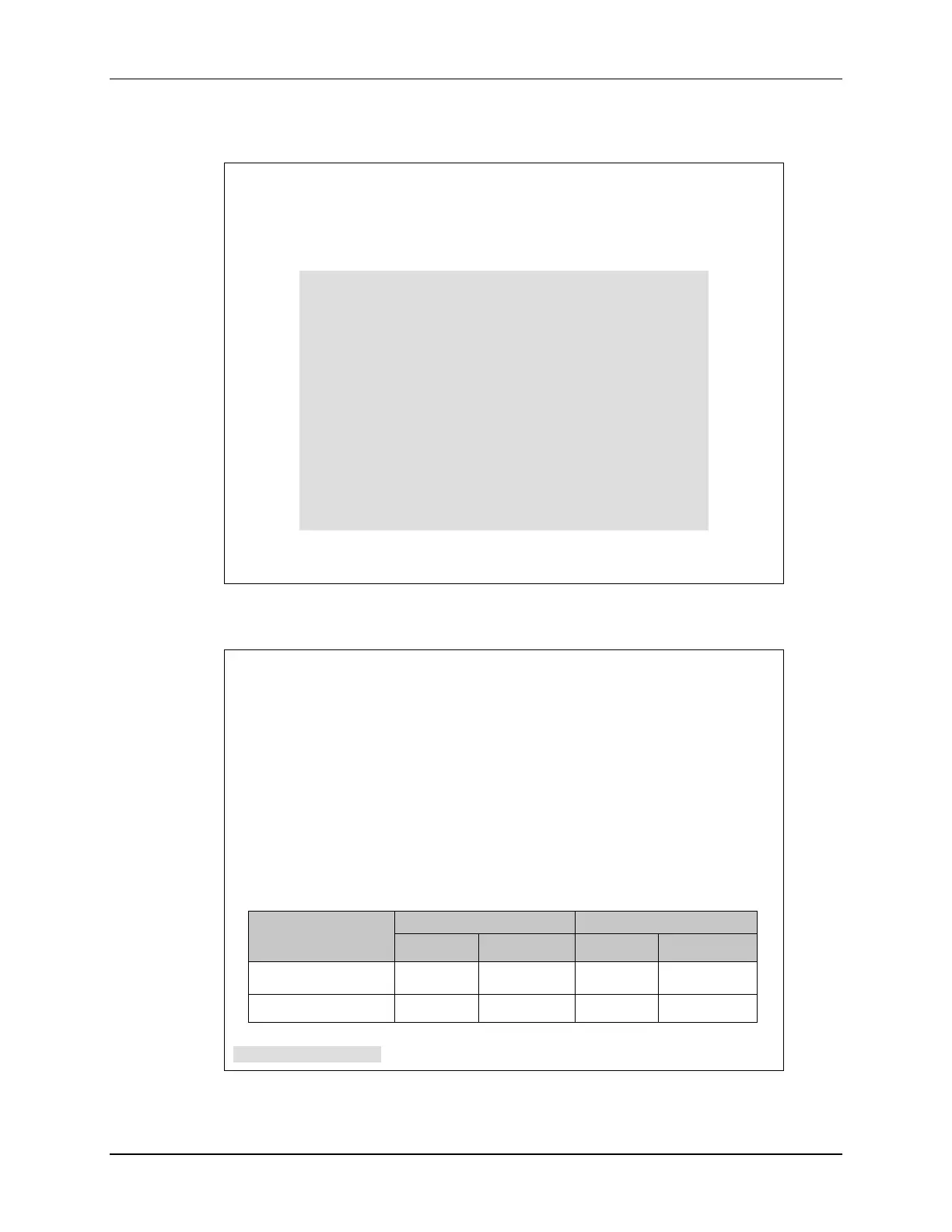

IPC Global Shared RAM and Message RAM

Global Shared RAM

Device contains up to 16 blocks of global shared RAM

Blocks named GS0 – GS15

Each block size is 4K words

Each block can configured to be used by CPU1 or CPU2

Selected by MemCfgRegs.GSxMSEL register

Individual memory blocks can be shared between the

CPU and DMA

Ownership

CPU1 Subsystem CPU2 Subsystem

CPU1 CPU1.DMA CPU2 CPU2.DMA

CPU1 Subsystem* R/W/Exe R/W R R

CPU2 Subsystem R R R/W/Exe R/W

* default

Note: register lock protected

Loading...

Loading...