Inter-Processor Communications

11 - 4 TMS320F2837xD Microcontroller Workshop - Dual-Core Inter-Processor Communications

There are up to 16 blocks of shared RAM on F2837xD devices. These shared RAM blocks are

typically used by the application, but can also be used for transferring messages and data.

Each block can individually be owned by either CPU1 or CPU2.

CPU1 core ownership:

At reset, CPU1 owns all of the shared RAM blocks. In this configuration CPU1 core can freely

use the memory blocks. CPU1 can read, write or execute from the block and CPU1.DMA can

read or write.

On the CPU2 core, CPU2 and CPU2.DMA can only read from these blocks. Blocks owned by the

CPU1 core can be used by the CPU1 to send CPU2 messages. This is referred to as “C1toC2”.

CPU2 core ownership:

After reset, the CPU1 application can assign ownership of blocks to the CPU2 subsystem. In this

configuration, CPU2 core can freely use the blocks. CPU2 can read, write or execute from the

block and the CPU2.DMA can read or write. CPU1 core, however can only read from the block.

Blocks owned by CPU2 core can be used can be used to send messages from the CPU2 to

CPU1. This is referred to as “C2toC1”.

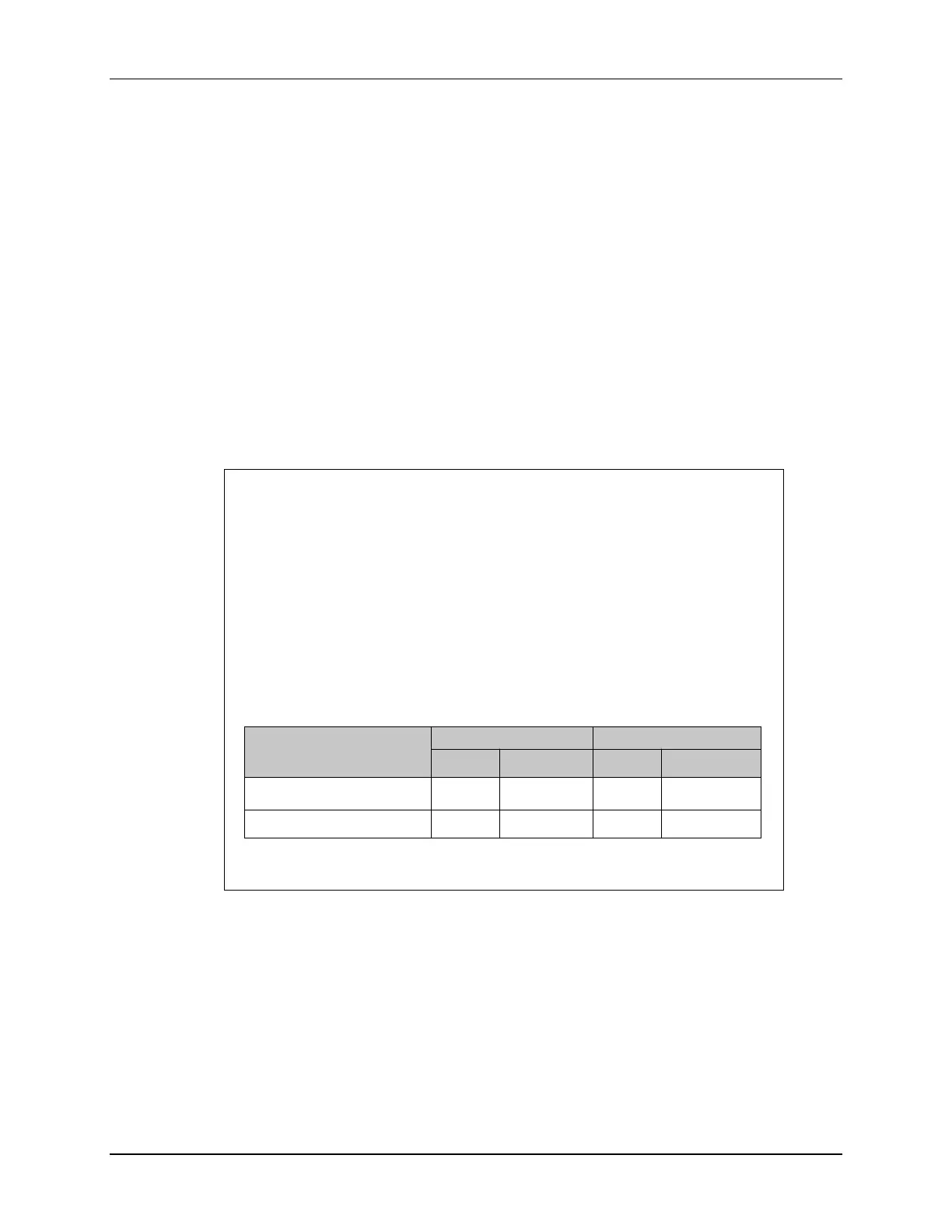

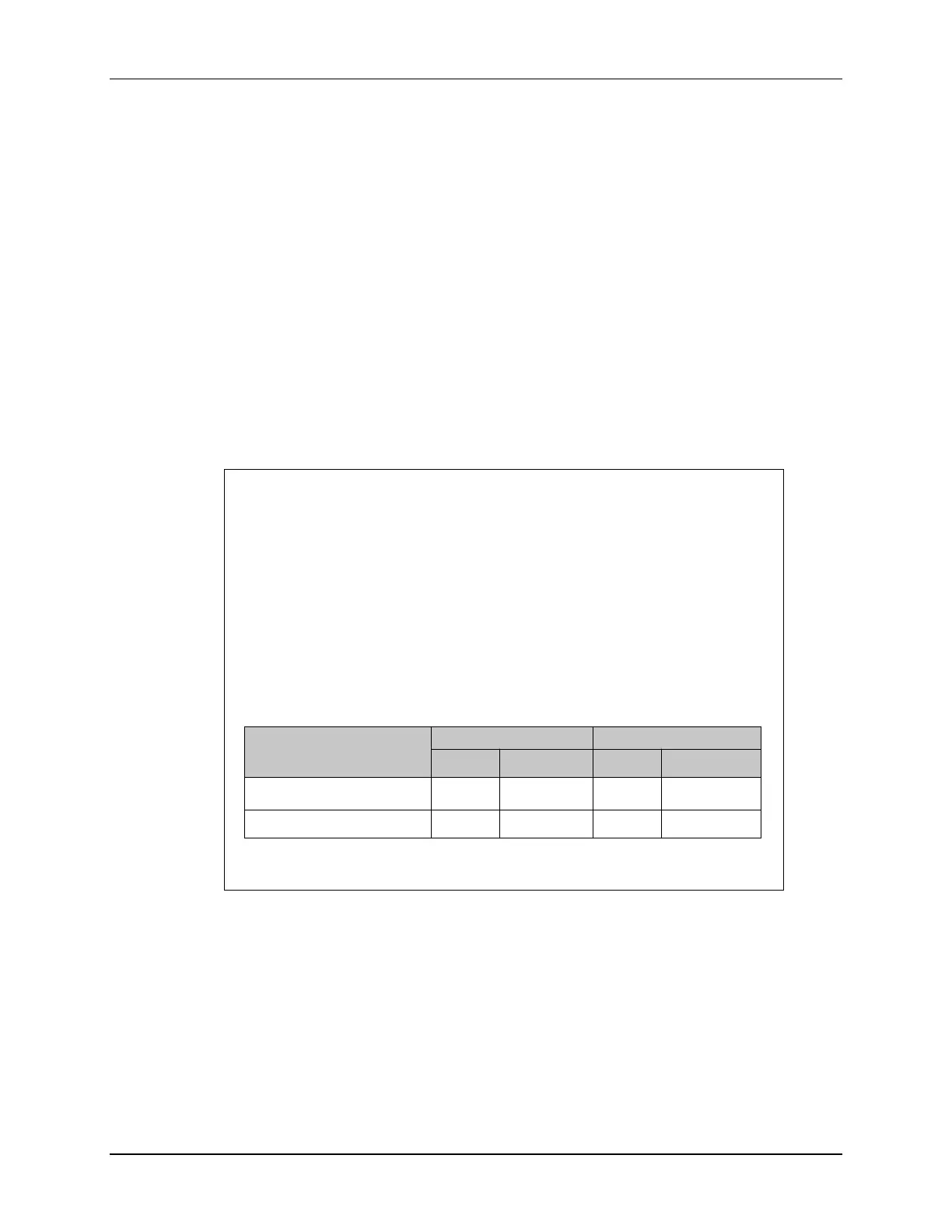

IPC Message RAM

Device contains 2 blocks of Message RAM

Each block size is 1K words

Each block is always enabled and the

configuration is fixed

Used to transfer messages or data between

CPU1 and CPU2

Message RAM

CPU1 Subsystem CPU2 Subsystem

CPU1 CPU1.DMA CPU2 CPU2.DMA

CPU1 to CPU2 (“C1toC2”) R/W R/W R R

CPU2 to CPU1 (“C2toC1”) R R R/W R/W

The F2837xD has two dedicated message RAM blocks. Each block is 1K words in length. Unlike

the shared RAM blocks, these blocks provide communication in one direction only and cannot be

reconfigured.

CPU1 to CPU2 “C1toC2” message RAM:

The first message RAM is the CPU1 to CPU2 or C1toC2. This block can be read or written to by

the CPU1 and read by the CPU2. CPU1 can write a message to this block and then the CPU2

can read it.

CPU2 to CPU1 “C2toC1” message RAM:

The second message RAM is the CPU2 to CPU1 or C2toC1. This block can be read or written to

by CPU2 and read by CPU1. This means CPU2 can write a message to this block and then

Loading...

Loading...