Inter-Processor Communications

TMS320F2837xD Microcontroller Workshop - Dual-Core Inter-Processor Communications 11 - 7

IPC Data Transfer

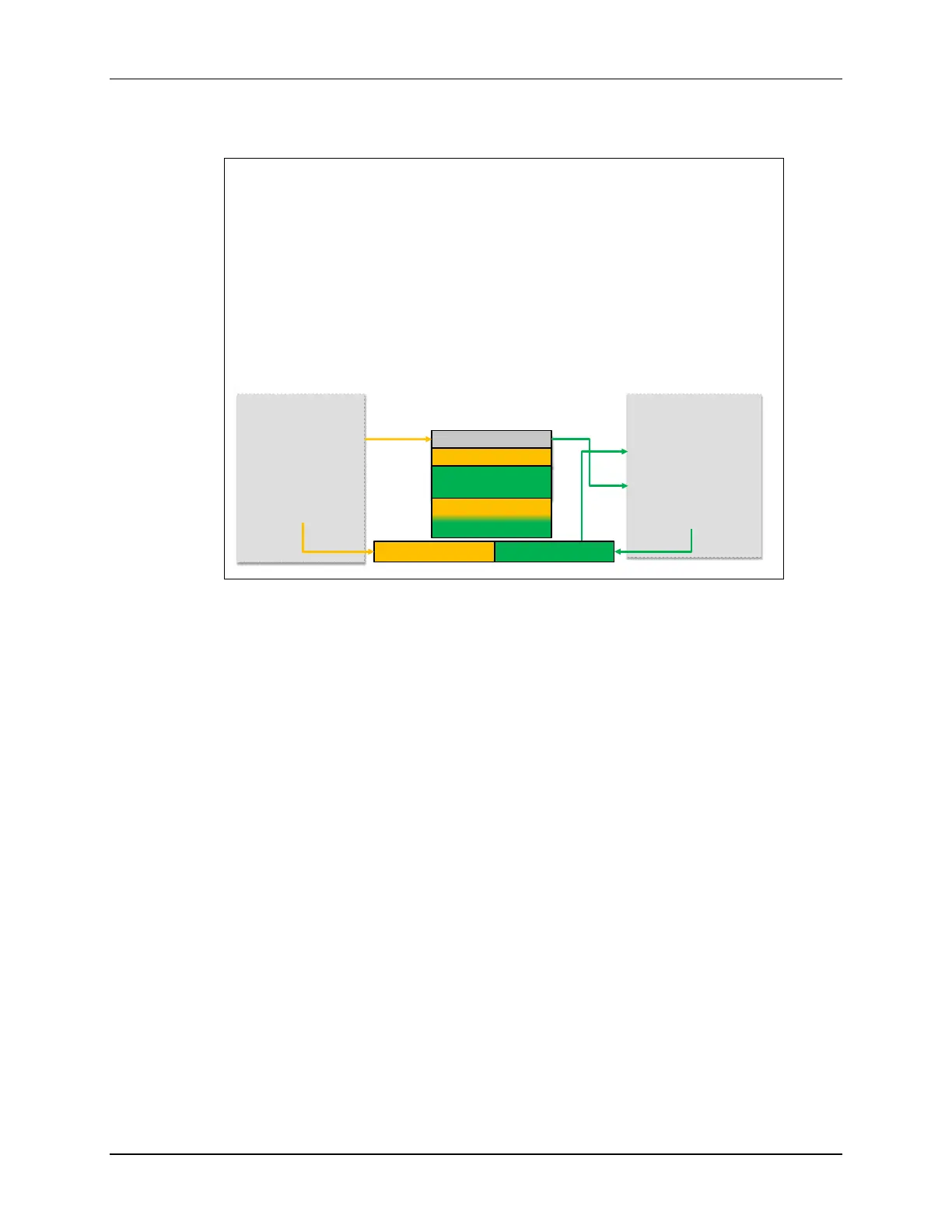

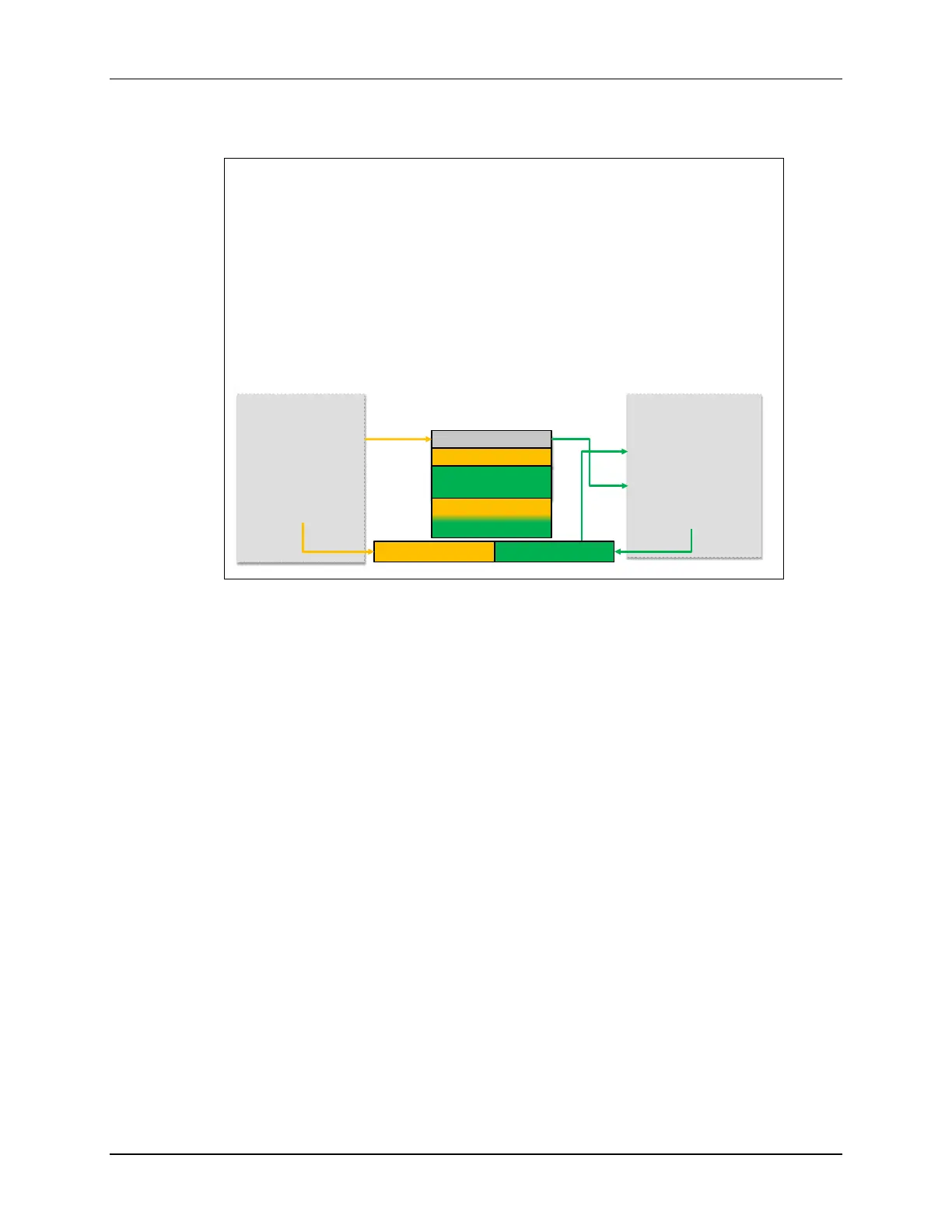

Basic IPC Data Transfer

Basic option – no software drivers needed

and easy to use!

Use the Message RAMs or global shared RAMs to

transfer data between processors at a known

address

Use the IPC flag registers to tell the other

processor that the data is ready

C1toC2 MSG RAM

C2toC1 MSG RAM

GSx Shared

RAM’s

CPU1 Application

CPU2 Application

Message

1: Write a message to

C1toC2 MSG RAM

C1TOC2IPCFLG C1TOC2IPCSTS

2: Write 1 to

C1TOC2IPCSET bit

3: sees C1TOC2IPCSTS

bit is set

4: read message

5: write 1 to

C1TOC2IPCACK bit

The F2837xD IPC is very easy to use. At the most basic level, the application does not need any

separate software drivers to communicate between processors. It can utilize the message RAM’s

and shared RAM blocks to pass data between processors at a fixed address known to both

processors. Then the sending processor can use the IPC flag registers merely to flag to the

receiving processor that the data is ready. Once the receiving processor has grabbed the data, it

will then acknowledge the corresponding IPC flag to indicate that it is ready for more messages.

As an example:

1. First, CPU1 would write a message to the CPU2 in C1toC2 MSG RAM.

2. Then the CPU1 would write a 1 to the appropriate flag bit in the C1TOC2IPCSET

register. This sets the C1TOC2IPCFLG, which also sets the C1TOC2IPCSTS register on

CPU2, letting CPU2 know that a message is available.

3. Then CPU2 sees that a bit in the C1TOC2IPCSTS register is set.

4. Next CPU2 reads the message from the C1toC2 MSG RAM and then

5. It writes a 1 to the same bit in the C1TOC2IPCACK register to acknowledge that it has

received the message. This subsequently clears the flag bit in C1TOC2IPCFLG and

C1TOC2IPCSTS.

6. CPU1 can then send more messages using that particular flag bit.

Loading...

Loading...