Inter-Processor Communications

11 - 6 TMS320F2837xD Microcontroller Workshop - Dual-Core Inter-Processor Communications

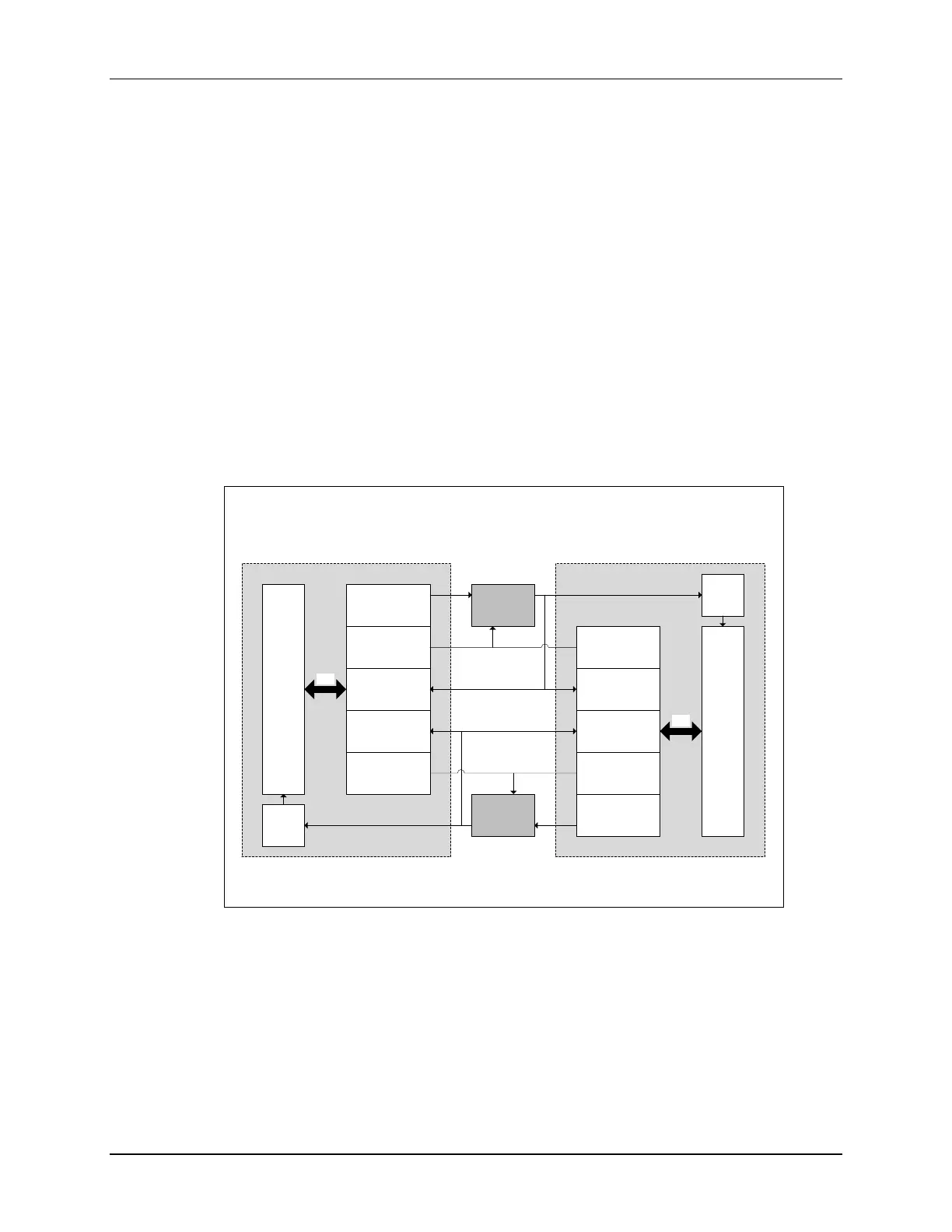

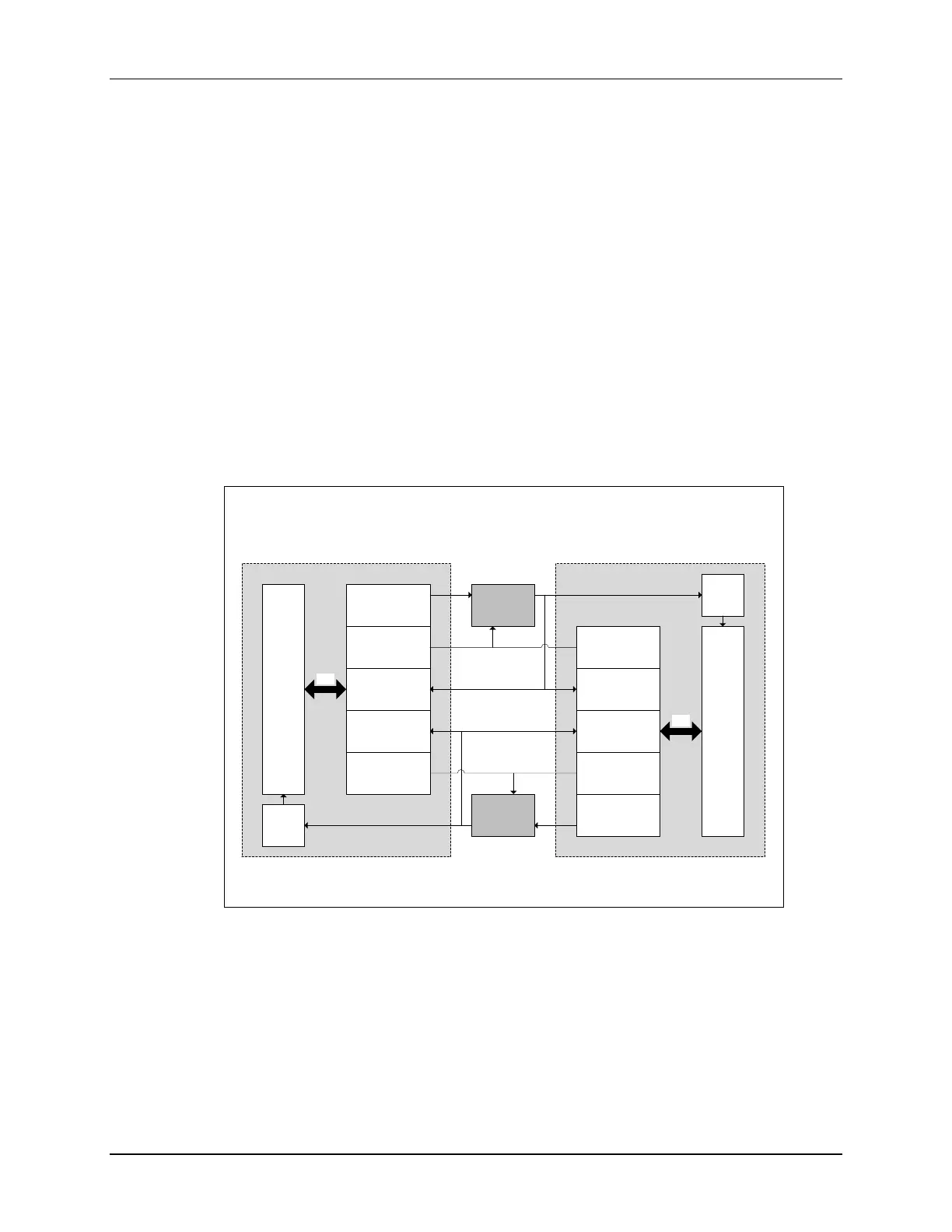

When the sending CPU wants to inform the receiver that a message is ready, it can make use of

an interrupt or flag. There are identical IPC interrupt and flag resources on both CPU1 core and

CPU2 core.

4 Interrupts:

There are 4 interrupts that CPU1 can send to CPU2 (and vice-versa) through the Peripheral

Interrupt Expansion (PIE) module. Each of the interrupts has a dedicated vector within the PIE,

IPC0 – IPC3.

28 Flags:

In addition, there are 28 flags available to each of the CPU cores. These flags can be used for

messages that are not time critical or they can be used to send status back to originating

processor. The flags and interrupts can be used however the application sees fit and are not tied

to particular operation in hardware.

Registers: Set, Flag, Clear, Status and Acknowledge

The registers to control the IPC interrupts and flags are 32-bits:

Bits [3:0] = interrupt & flag

Bits [31:4] = flag only

Messaging with IPC Flags and Interrupts

CPU

2 Memory Map

CPU1 Memory Map

IPCCLR

IPCFLG IPCSTS

IPCACK

IPCSET

IPCCLR

IPCFLG CPU2

Set

Clear

Q

PIE

(IPC0-3)

PIE

(IPC0-3)

CPU1

Set

Clear

Q

IPCSTS

IPCACK

IPC Registers

IPCSET

IPC Registers

R/W

R/W

CPU1 to CPU2

CPU2 to CPU1

Loading...

Loading...