Basic Flash Operation

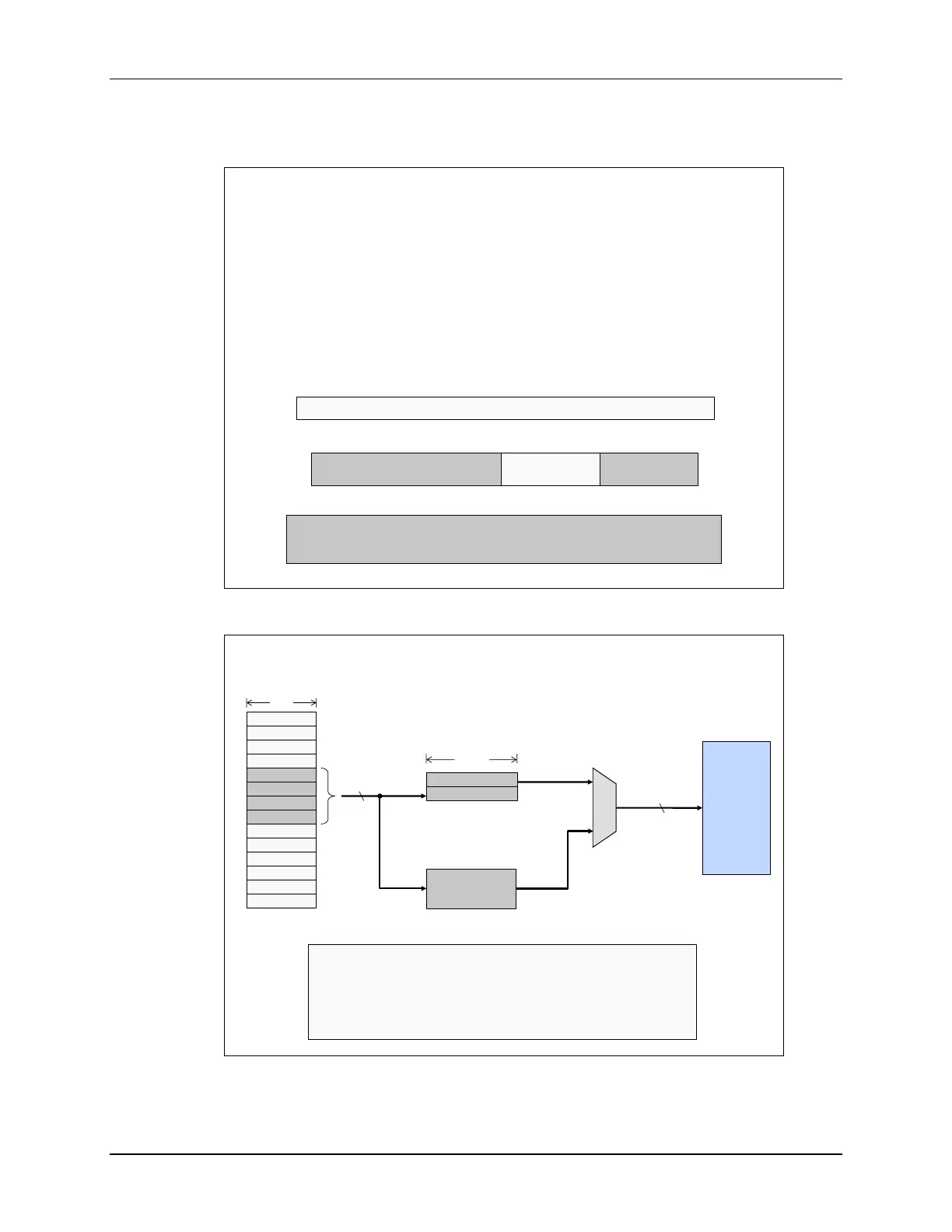

RWAIT bit-field in the FRDCNTL register specifies the number of

random accesses wait states

OTP reads are hardwired for 10 wait states (RWAIT has no effect)

Must specify the number of SYSCLK cycle wait-states;

Reset defaults are maximum value (15)

Flash/OTP reads returned after (RWAIT + 1 SYSCLK cycles)

Flash configuration code should not be run from the Flash memory

FlashCtrlRegs.FRDCNTL.bit.RWAIT = 0x3; // Setting for 200 MHz

reserved

31

0

8 7

RWAIT

reserved

12 11

*** Refer to the F28x7x datasheet for detailed numbers ***

For 200 MHz, RANDWAIT = 3

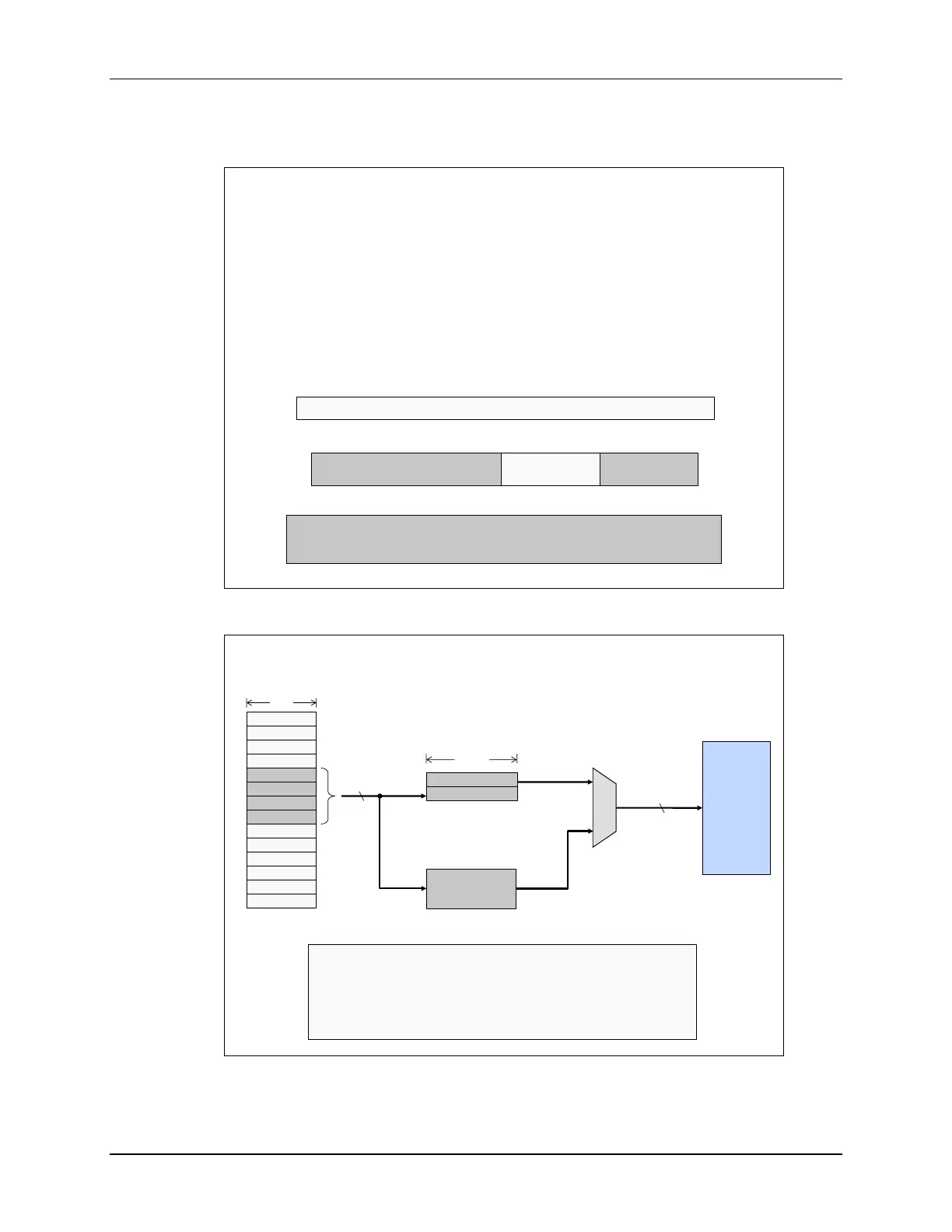

Speeding Up Execution in Flash / OTP

Enable prefetch mechanism:

FlashCtrlRegs.FRD_INTF_CTRL.bit.PREFETCH_EN = 1;

Enable data cache:

FlashCtrlRegs.FRD_INTF_CTRL.bit.DATA_CACHE_EN = 1;

16 or 32

dispatched

16

128

Aligned

128-bit

fetch

2-level deep

fetch buffer

128

C28x

core

decoder

unit

128-bit data

cache

MUX

Instruction

fetch

Data read either from

program or data memory

Flash or OTP

Loading...

Loading...