Flash Configuration and Memory Performance

10 - 8 TMS320F2837xD Microcontroller Workshop - System Design

Code Execution Performance

Assume 200 MHz SYSCLKOUT and single-cycle

execution for each instruction

Internal RAM: 200 MIPS

Fetch up to 32 bits every cycle 1 instruction/cycle

Flash: 200 MIPS

Assume RWAIT=3, prefetch buffer enabled

Fetch 128 bits every 4 cycles:

(128 bits) / (32-bits per instruction worst-case) 4 instructions/4 cycles

PC discontinuity will degrade this, while 16-bit instructions can help

Benchmarking in control applications has shown actual performance of about

90% efficiency, yielding approximately 180 MIPS

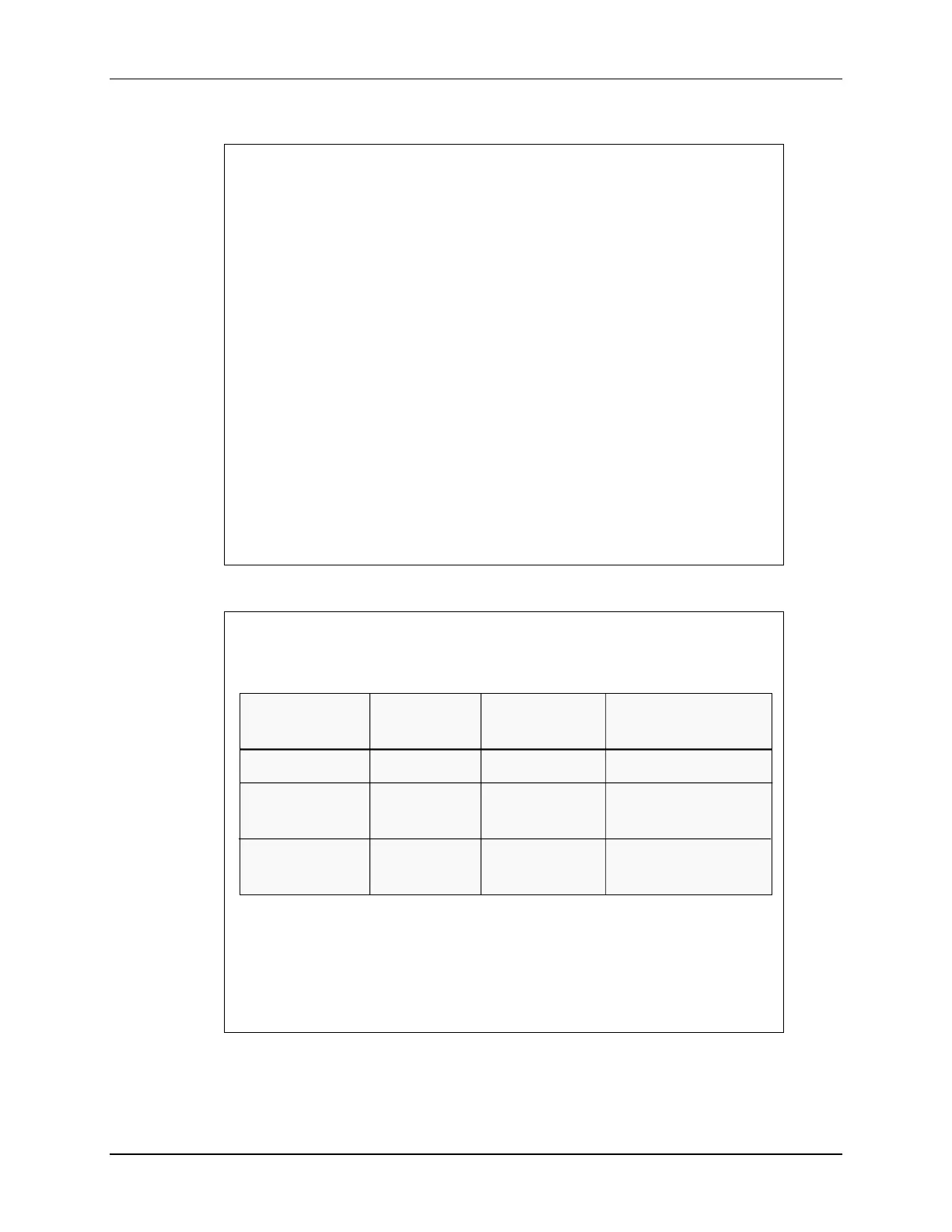

Data Access Performance

Assume 200 MHz SYSCLKOUT

Internal RAM has best data performance – put time critical data here

Flash performance often sufficient for constants and tables

Note that the flash instruction fetch pipeline will also stall during a

flash data access

For best flash performance, arrange data so that all 128 bits in a

cache line are utilized (e.g. sequential access)

Memory 16-bit access 32-bit access Notes

(words/cycle) (words/cycle)

Internal RAM 1 1

Flash 0.73 0.57

‘sequential’ access

(8 words/11 cycles) (4 words/7 cycles)

Flash 0.25 0.25

random access

(1 word/4 cycles) (1 word/4 cycles)

Assumes RWAIT = 3,

flash data cache enabled,

all 128 bits in cache are used

Assumes RWAIT = 3

Loading...

Loading...