Flash Configuration and Memory Performance

TMS320F2837xD Microcontroller Workshop - System Design 10 - 9

Flash / OTP Power Modes

Power configuration settings save power by putting Flash/OTP to

‘Sleep’ or ‘Standby’ mode; Flash will automatically enter ‘Active’

mode if a Flash/OTP access is made

At reset Flash/OTP is in sleep mode

Operates in three power modes:

Sleep (lowest power)

Standby (shorter transition time to active)

Active (highest power)

After an access is made, Flash/OTP can automatically power down

to ‘Standby’ or ‘Sleep’ (active grace period set in user

programmable counters)

Setting Flash charge pump fallback power mode to active:

FlashCtrlRegs.FPAC1.bit.PMPPWR = 0x1; // 0: sleep, 1: active

Setting fallback power mode to active:

FlashCtrlRegs.FBFALLBACK.bit.BNKPWR0 = 0x3; // 0: sleep, 1: standby,

// 2: reserved, 3: active

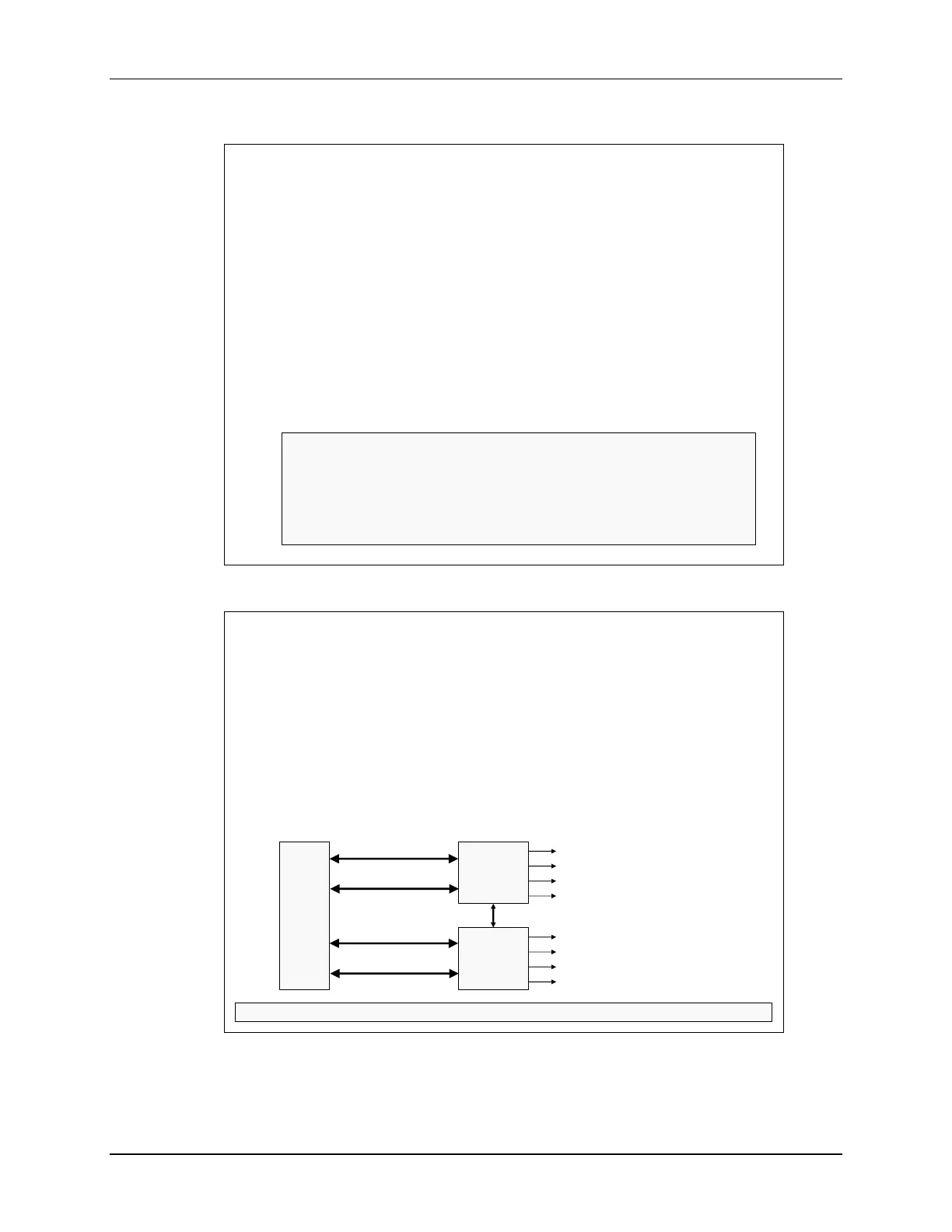

Error Correction Code (ECC) Protection

Provides capability to screen out Flash/OTP memory faults (enabled at reset)

Single error correction and double error detection (SECDED)

For every 64-bits of Flash/OTP, 8 ECC check bits are calculated and

programmed into ECC memory

ECC check bits are programmed along with Flash/OTP data

During an instruction fetch or data read operation the 64-bit data/8-bit ECC are

processed by the SECDED to determine one of three conditions:

No error occurred

A correctable error (single bit data error) occurred

A non-correctable error (double bit data error or address error) occurred

SECDED

Single-bit data error

Address/double-bit data error

Single-bit error position

Corrected data out

SECDED

Single-bit data error

Address/double-bit data error

Single-bit error position

Corrected data out

128-bit aligned

Flash

and

OTP

ECC (15:8)

Data (127:64)

ECC (7:0)

Data (63:0)

FlashEccRegs.ECC_ENABLE.bit.ENABLE = 0xA; // 0xA enable; other values disable

Loading...

Loading...