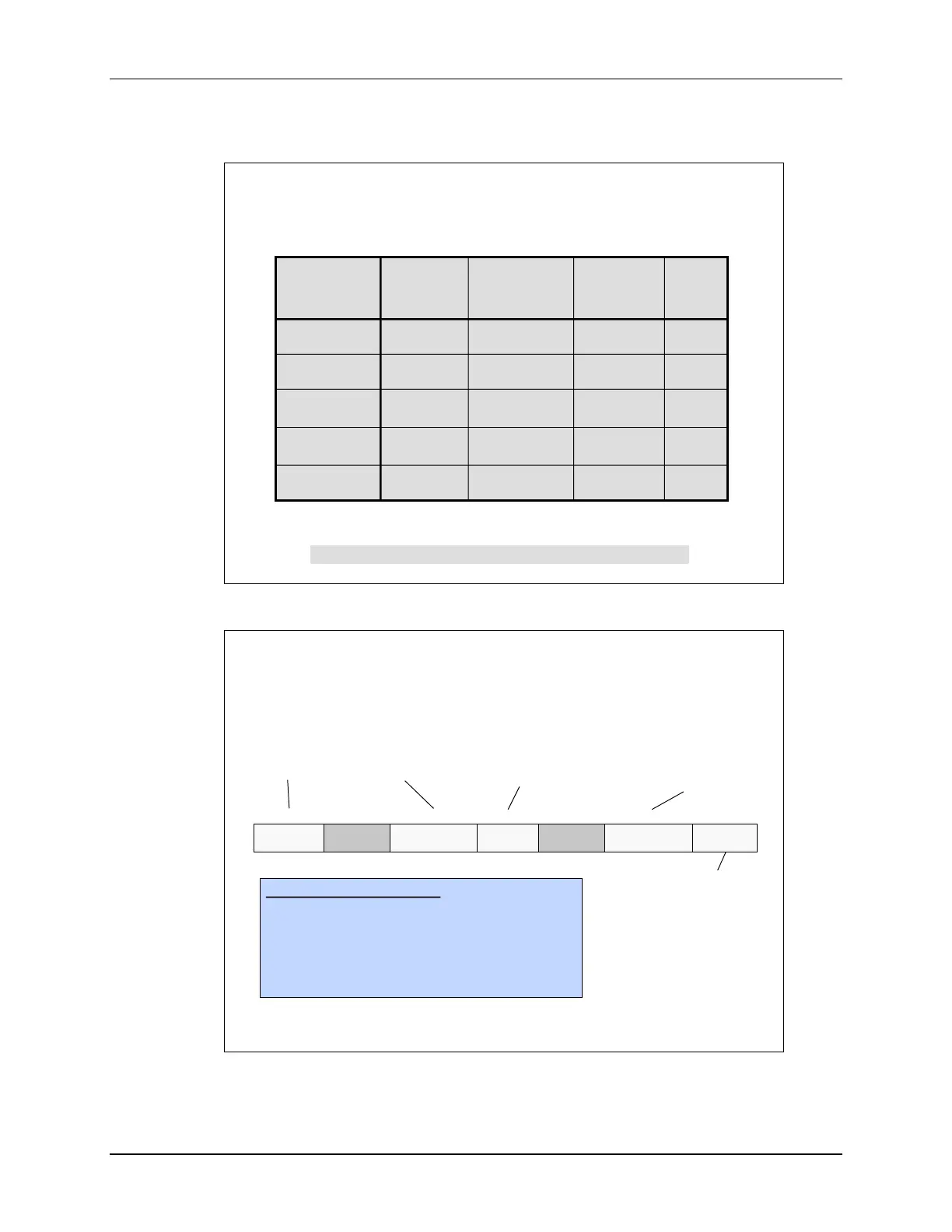

Low Power Modes

Low Power

Mode

CPU Logic

Clock

Peripheral

Logic Clock

Watchdog

Clock

PLL /

OSC

Normal Run

IDLE

STANDBY

HALT

HIB *

on

off

off

off

off

on

on

off

off

off

on

on

on

off

off

on

on

on

off

off

See device datasheet for power consumption in each mode

* Hibernate - low power data retention via M0 and M1 memories

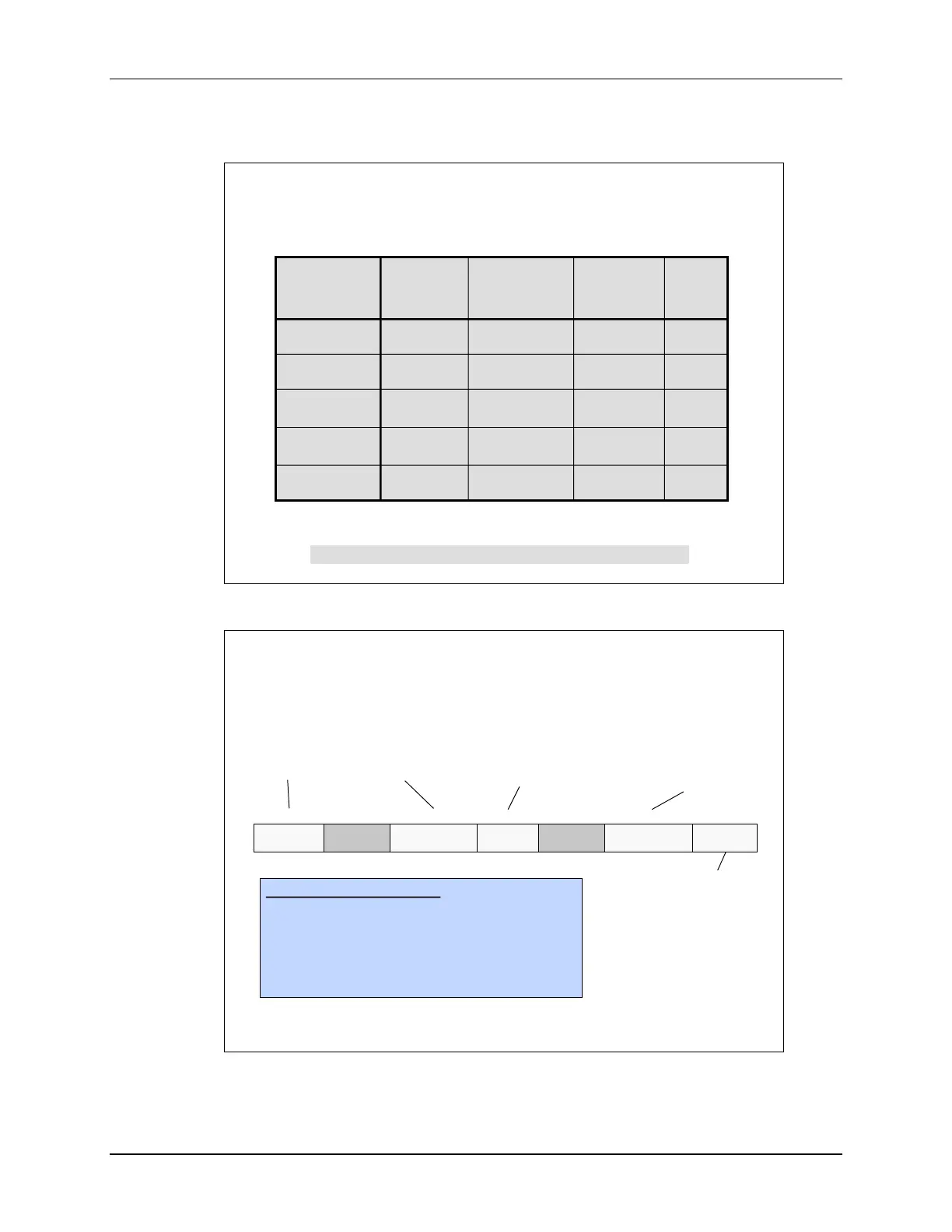

Low Power Mode Control Register

SysCtrlRegs.LPMCR (lab file: SysCtrl.c)

1 - 07 - 214 - 8

LPM0WDINTE QUALSTDBYreserved

Low Power

Mode Selection

00 = IDLE (default)

01 = STANDBY

10 = HALT

11 = HIB (Hibernate)

Wake from STANDBY

GPIO signal qualification *

000000 = 2 OSCCLKs

000001 = 3 OSCCLKs

111111 = 65 OSCCLKs (default)

.

.

.

.

.

.

.

.

.

15

Watchdog Interrupt

wake device from

STANDBY

0 = disable (default)

1 = enable

Low Power Mode Entering

1. Set LPM bits

2. Enable desired exit interrupt(s)

3. Execute IDLE instruction

4. The power down sequence of the hardware

depends on LP mode

* QUALSTDBY will qualify the GPIO wakeup signal in series with the GPIO port qualification.

This is useful when GPIO port qualification is not available or insufficient for wake-up purposes.

M0M1MODEIOISODIS reserved

17 - 1630 - 1831

State of CPUx M0

& M1 memories in

HIB mode

00 = on (default)

01 = off

IO ISOLATION in

HIB mode set by

H/W (CPU1 only)

0 = off (default)

1 = on

Loading...

Loading...