ePWM

7 - 10 TMS320F2837xD Microcontroller Workshop - Control Peripherals

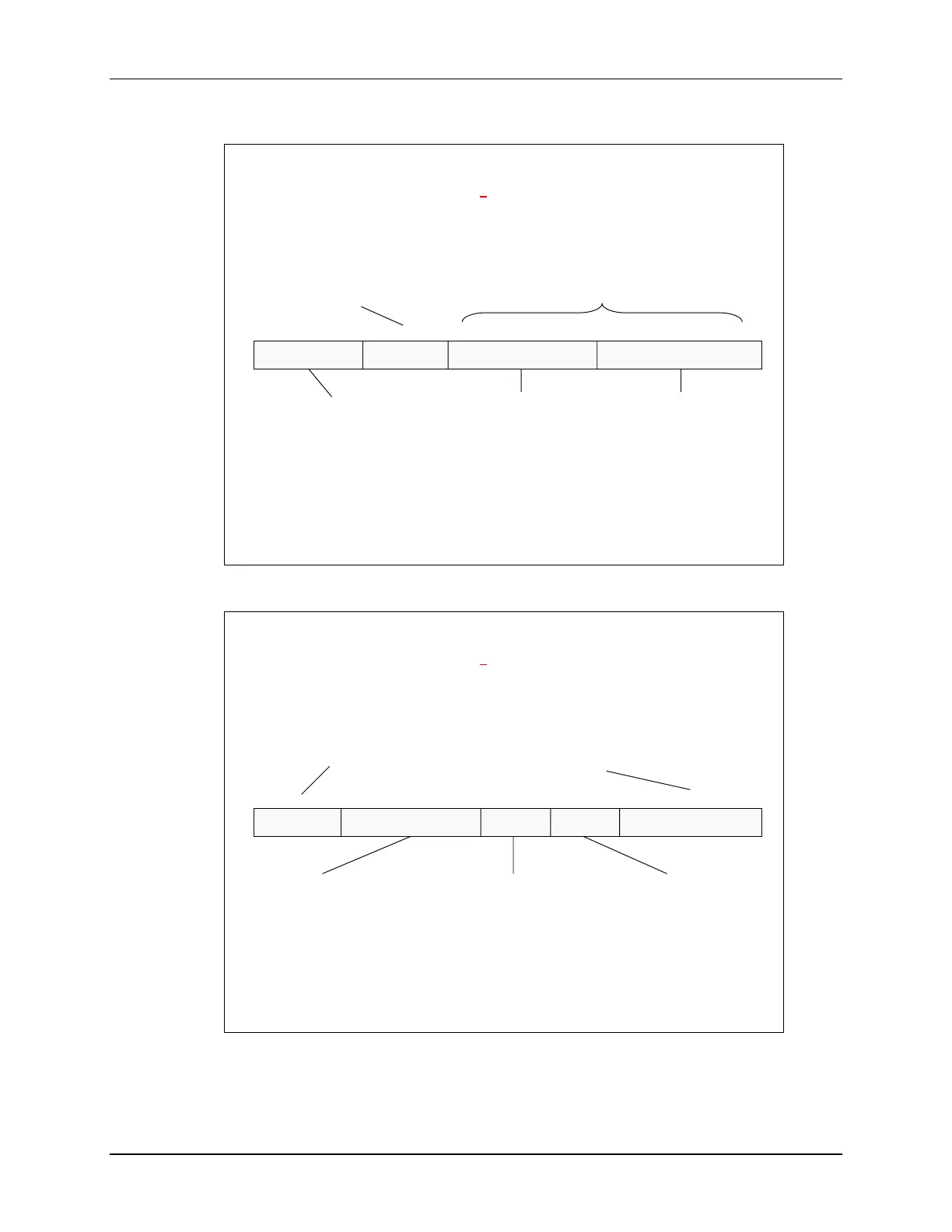

ePWM Time-Base Control Register

EPwmxRegs.TBCTL

Upper Register:

FREE_SOFT PHSDIR CLKDIV HSPCLKDIV

15 - 14 13 12 - 10 9 - 7

TBCLK = EPWMCLK / (HSPCLKDIV * CLKDIV)

TB Clock Prescale

000 = /1 (default)

001 = /2

010 = /4

011 = /8

100 = /16

101 = /32

110 = /64

111 = /128

High Speed TB

Clock Prescale

000 = /1

001 = /2 (default)

010 = /4

011 = /6

100 = /8

101 = /10

110 = /12

111 = /14

Emulation Halt Behavior

00 = stop after next CTR inc/dec

01 = stop when:

Up Mode; CTR = PRD

Down Mode; CTR = 0

Up/Down Mode; CTR = 0

1x = free run (do not stop)

Phase Direction

0 = count down after sync

1 = count up after sync

(HSPCLKDIV is for legacy compatibility)

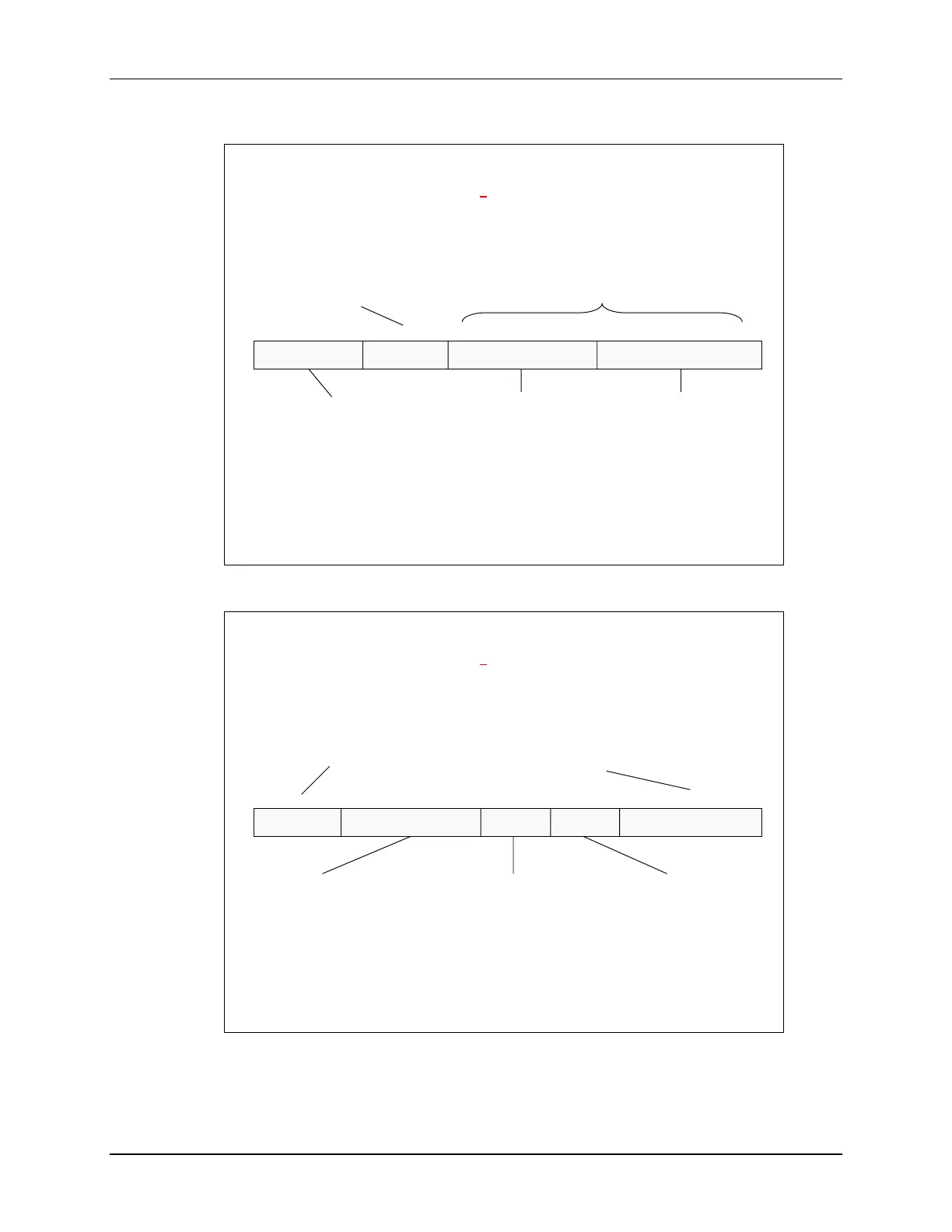

ePWM Time-Base Control Register

EPwmxRegs.TBCTL

Lower Register:

CTRMODESWFSYNC SYNCOSEL PRDLD PHSEN

6 5 - 4 3 1 - 02

Software Force Sync Pulse

0 = no action

1 = force one-time sync

Sync Output Select

(source of EPWMxSYNC0 signal)

00 = EPWMxSYNCI

01 = CTR = 0

10 = CTR = CMPB *

11 = disable SyncOut

Counter Mode

00 = count up

01 = count down

10 = count up and down

11 = stop – freeze (default)

Period Shadow Load

0 = load on CTR = 0

1 = load immediately

Phase Reg. Enable

0 = disable

1 = CTR = TBPHS on

EPWMxSYNCI signal

* CMPC and CMPD option

available in TBCTL2 register

Loading...

Loading...