ePWM

TMS320F2837xD Microcontroller Workshop - Control Peripherals 7 - 39

These event triggers can occur when the time-base counter equals zero, period, zero or period,

the up or down count match of a compare register. Recall that the digital-compare subsystem

can also generate an ADC start of conversion based on one or more compare events. Notice

counter up and down are independent and separate.

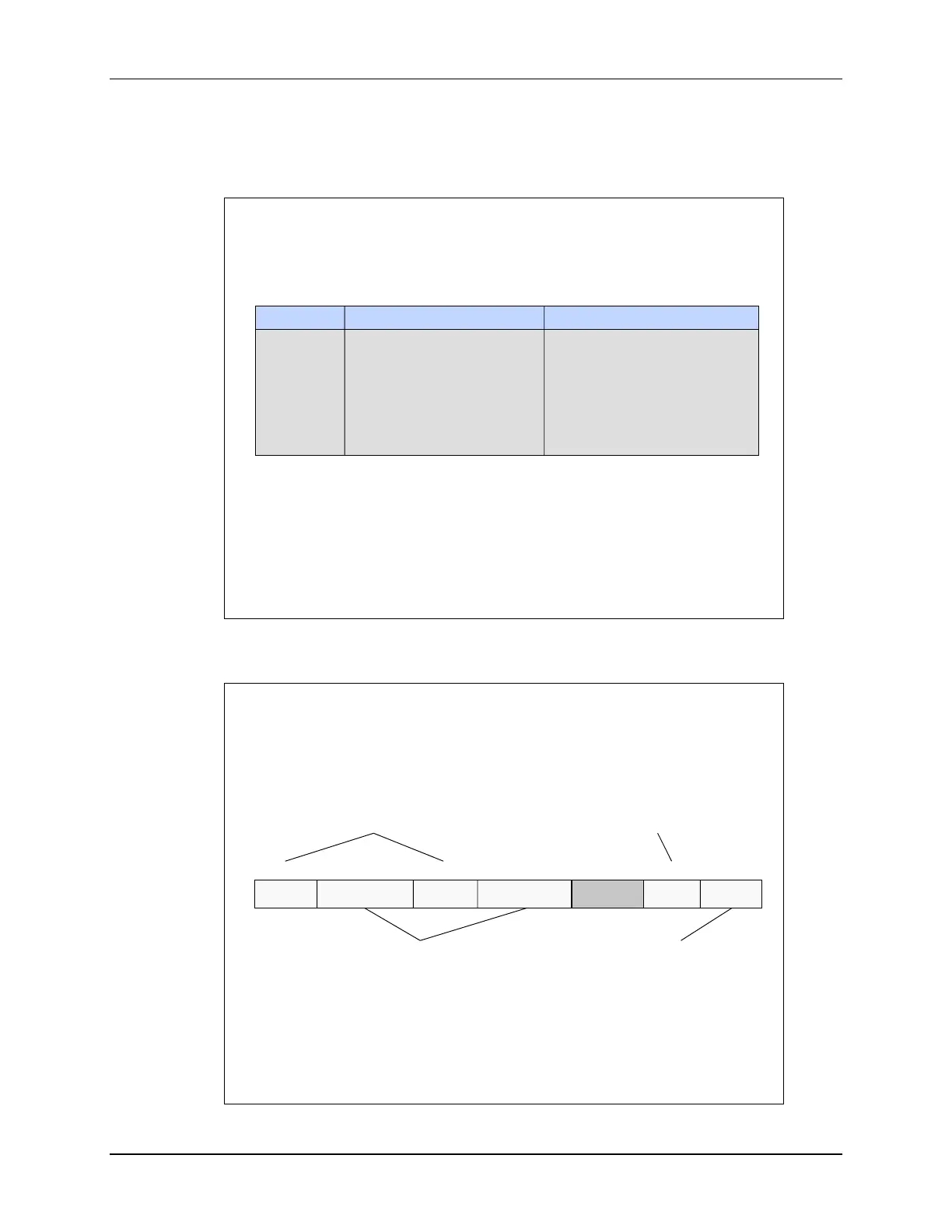

Name Description Structure

ETSEL Event-Trigger Selection EPwmxRegs.ETSEL.all =

ETPS Event-Trigger Pre-Scale EPwmxRegs.ETPS.all =

ETFLG Event-Trigger Flag EPwmxRegs.ETFLG.all =

ETCLR Event-Trigger Clear EPwmxRegs.ETCLR.all =

ETFRC Event-Trigger Force EPwmxRegs.ETFRC.all =

ePWM Event-Trigger Sub-Module

Registers

(lab file: EPwm.c)

Refer to the Technical Reference Manual for a complete listing of registers

The event-trigger submodule also incorporates pre-scaling logic to issue an interrupt request or

ADC start of conversion at every event or up to every fifteenth event.

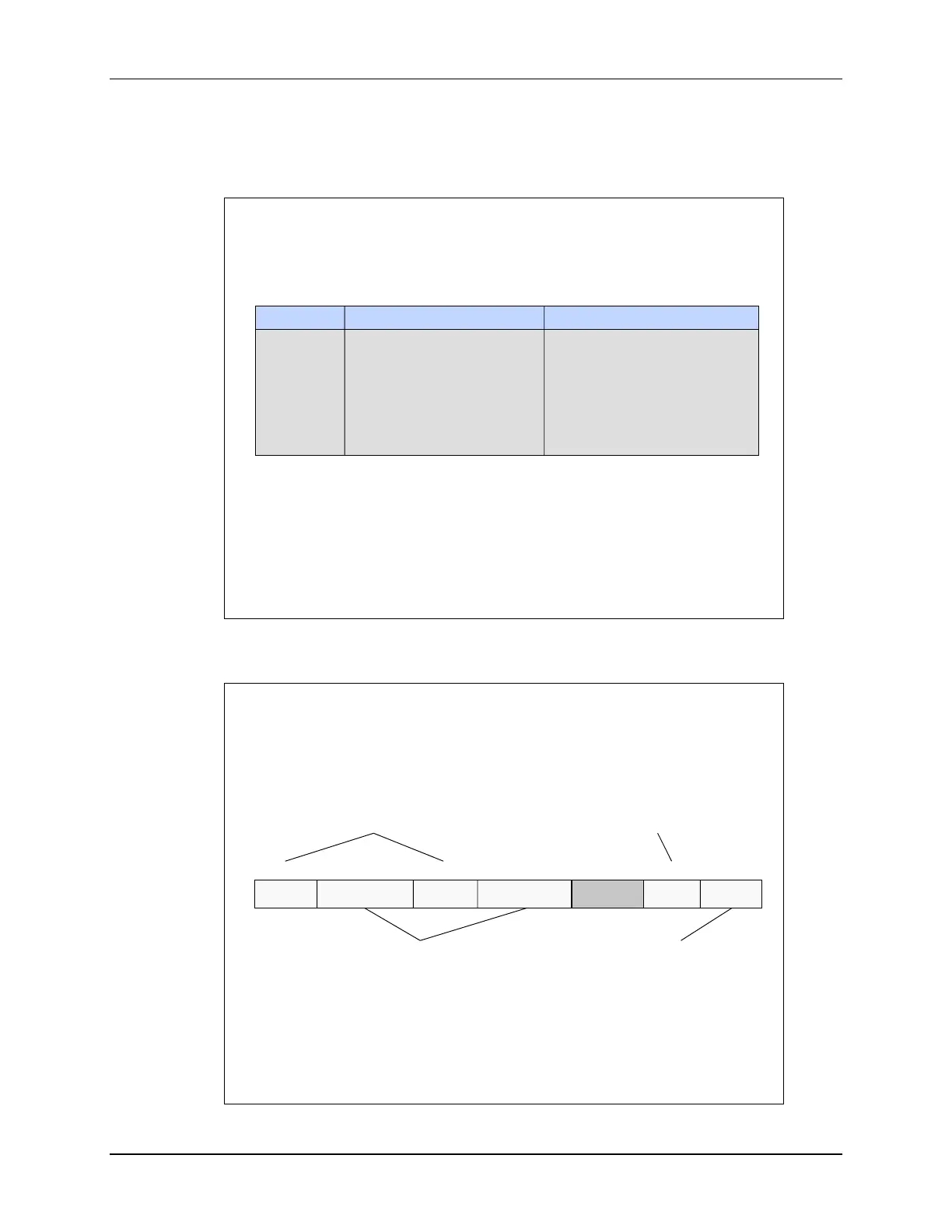

ePWM Event-Trigger Selection Register

EPwmxRegs.ETSEL

15 11 7 - 4 2 - 0

INTEN INTSEL

reserved

3

SOCBSEL

SOCASEL

SOCAENSOCBEN

10 - 814 - 12

Enable SOCB / A

0 = disable

1 = enable

EPWMxSOCB / A Select

000 = DCBEVT1 / DCAEVT1

001 = CTR = 0

010 = CTR = PRD

011 = CTR = 0 or PRD

100 = CTRU = CMPA

101 = CTRD = CMPA

110 = CTRU = CMPB

111 = CTRD = CMPB

Enable EPWMxINT

0 = disable

1 = enable

EPWMxINT Select

000 = reserved

001 = CTR = 0

010 = CTR = PRD

011 = CTR = 0 or PRD

100 = CTRU = CMPA

101 = CTRD = CMPA

110 = CTRU = CMPB

111 = CTRD = CMPB

Loading...

Loading...