eCAP

7 - 46 TMS320F2837xD Microcontroller Workshop - Control Peripherals

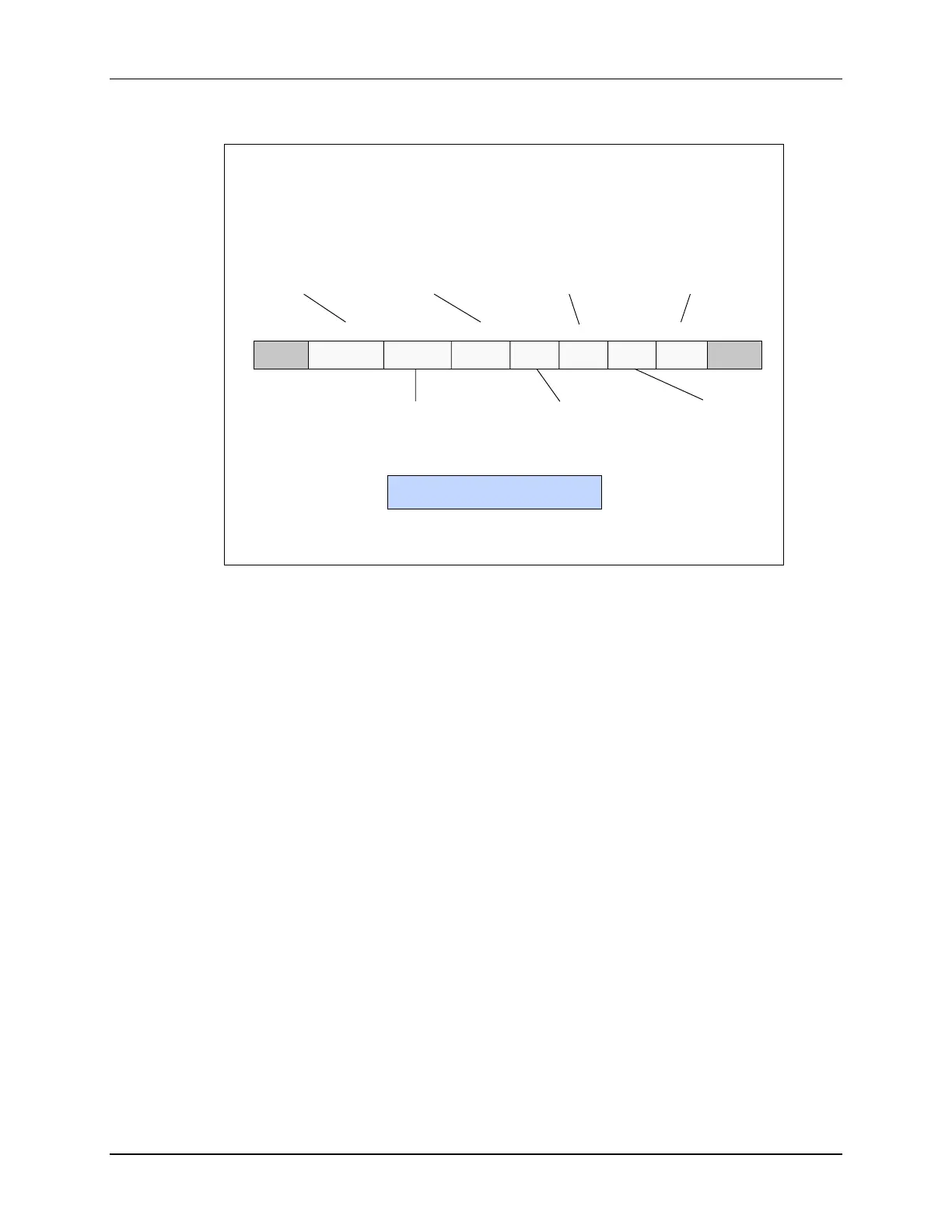

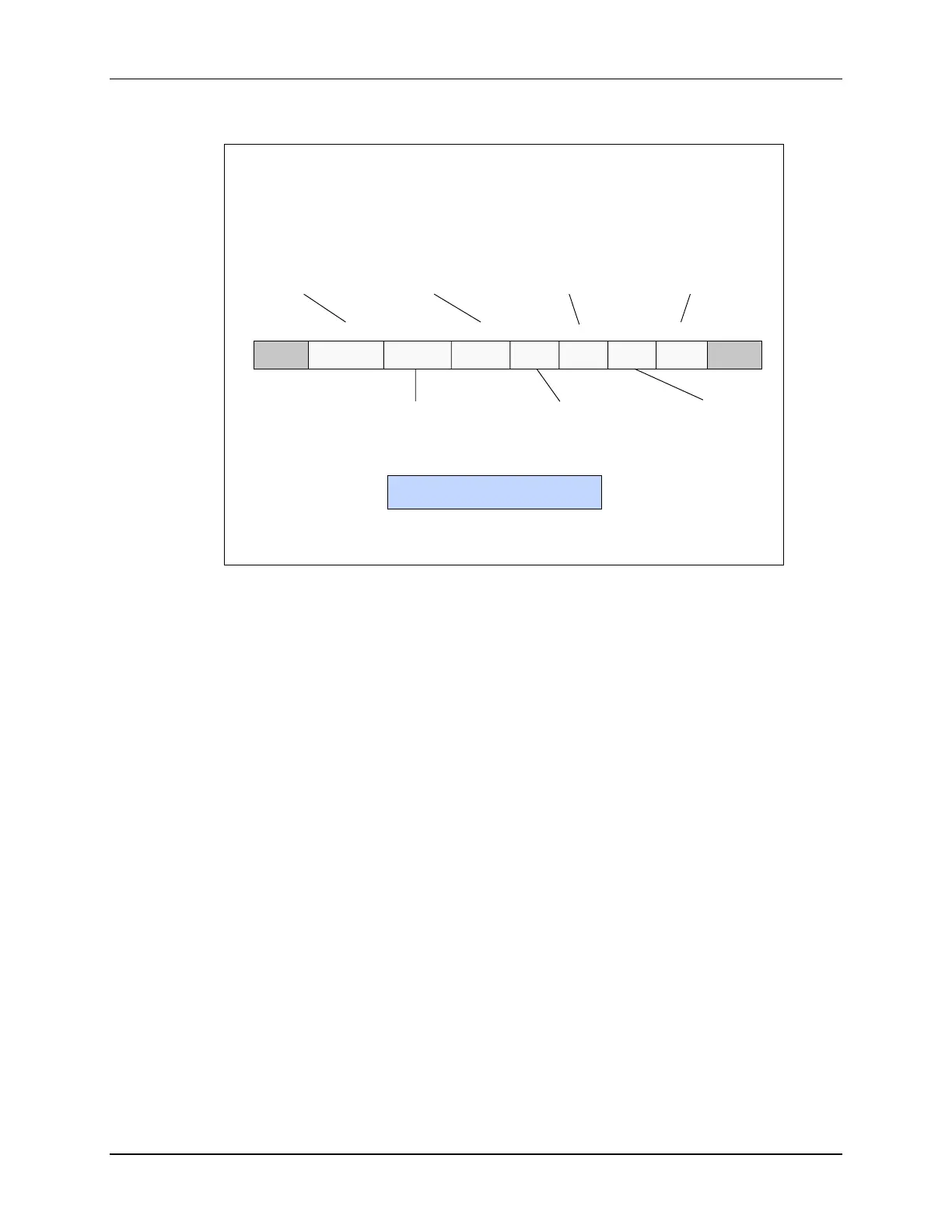

eCAP Interrupt Enable Register

ECapxRegs.ECEINT

CTR=CMP CTR=PRD

7 3 02

CTROVF CEVT4 CEVT3 CEVT2 CEVT1

1456

reserved

15 - 8

reserved

0 = disable as interrupt source

1 = enable as interrupt source

CTR = CMP

Interrupt Enable

CTR = PRD

Interrupt Enable

CTR = Overflow

Interrupt Enable

Capture Event 3

Interrupt Enable

Capture Event 1

Interrupt Enable

Capture Event 4

Interrupt Enable

Capture Event 2

Interrupt Enable

The capture unit interrupts offer immediate CPU notification of externally captured events. In

situations where this is not required, the interrupts can be masked and flag testing/polling can be

used instead. This offers increased flexibility for resource management. For example, consider a

servo application where a capture unit is being used for low-speed velocity estimation via a

pulsing sensor. The velocity estimate is not used until the next control law calculation is made,

which is driven in real-time using a timer interrupt. Upon entering the timer interrupt service

routine, software can test the capture interrupt flag bit. If sufficient servo motion has occurred

since the last control law calculation, the capture interrupt flag will be set and software can

proceed to compute a new velocity estimate. If the flag is not set, then sufficient motion has not

occurred and some alternate action would be taken for updating the velocity estimate. As a

second example, consider the case where two successive captures are needed before a

computation proceeds (e.g. measuring the width of a pulse). If the width of the pulse is needed

as soon as the pulse ends, then the capture interrupt is the best option. However, the capture

interrupt will occur after each of the two captures, the first of which will waste a small number of

cycles while the CPU is interrupted and then determines that it is indeed only the first capture. If

the width of the pulse is not needed as soon as the pulse ends, the CPU can check, as needed,

the capture registers to see if two captures have occurred, and proceed from there.

Loading...

Loading...