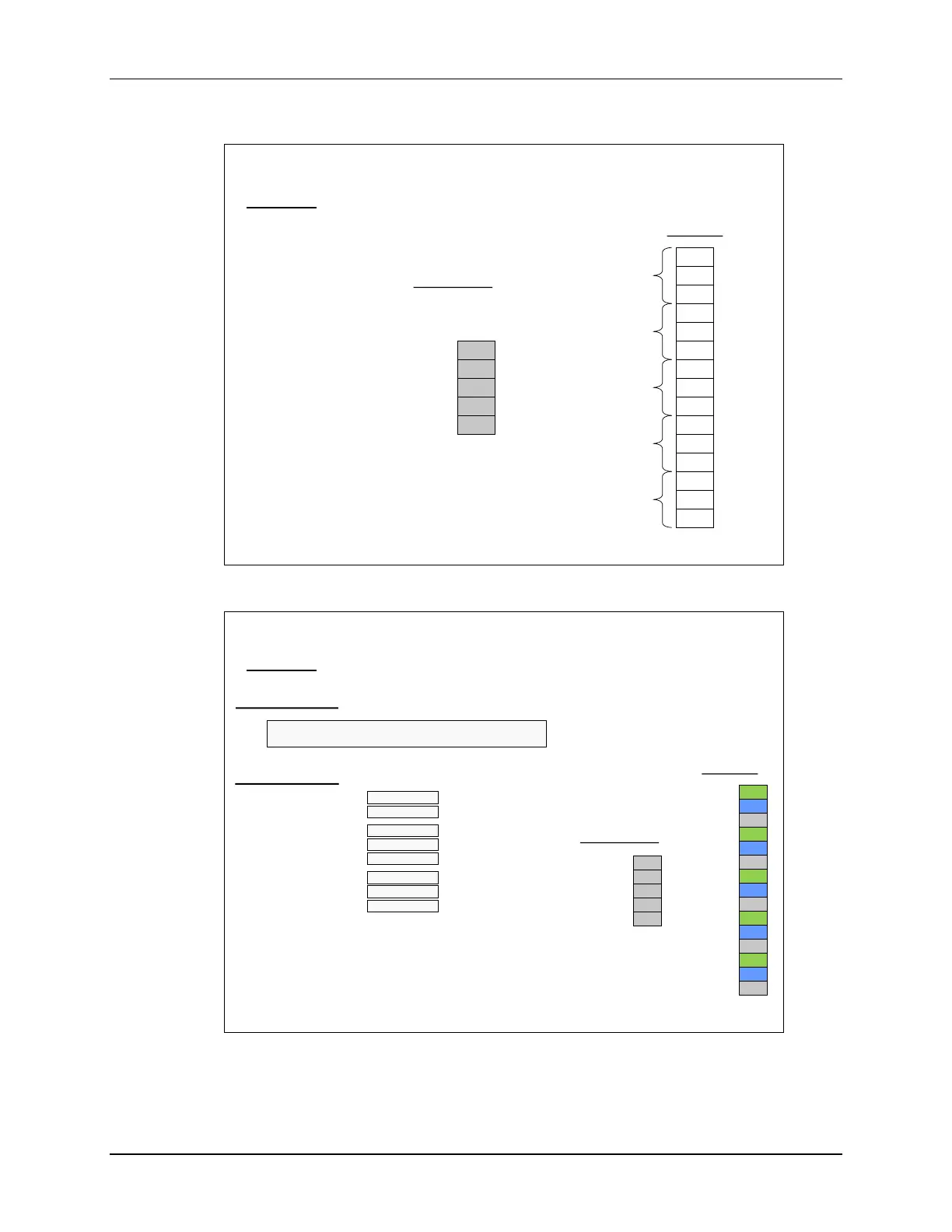

* Size registers are N-1

Data Binning Example Register Setup

BURST_SIZE*

TRANSFER_SIZE*

0x0004

5 words/burst

0x0002

3 bursts/transfer

SRC_ADDR_SHADOW

SRC_BURST_STEP

SRC_TRANSFER_STEP

0x00000B00

0x0001

DST_ADDR_SHADOW

DST_BURST_STEP

DST_TRANSFER_STEP

0x0003

0xFFF5

(-11)

0xFFFC

(-4)

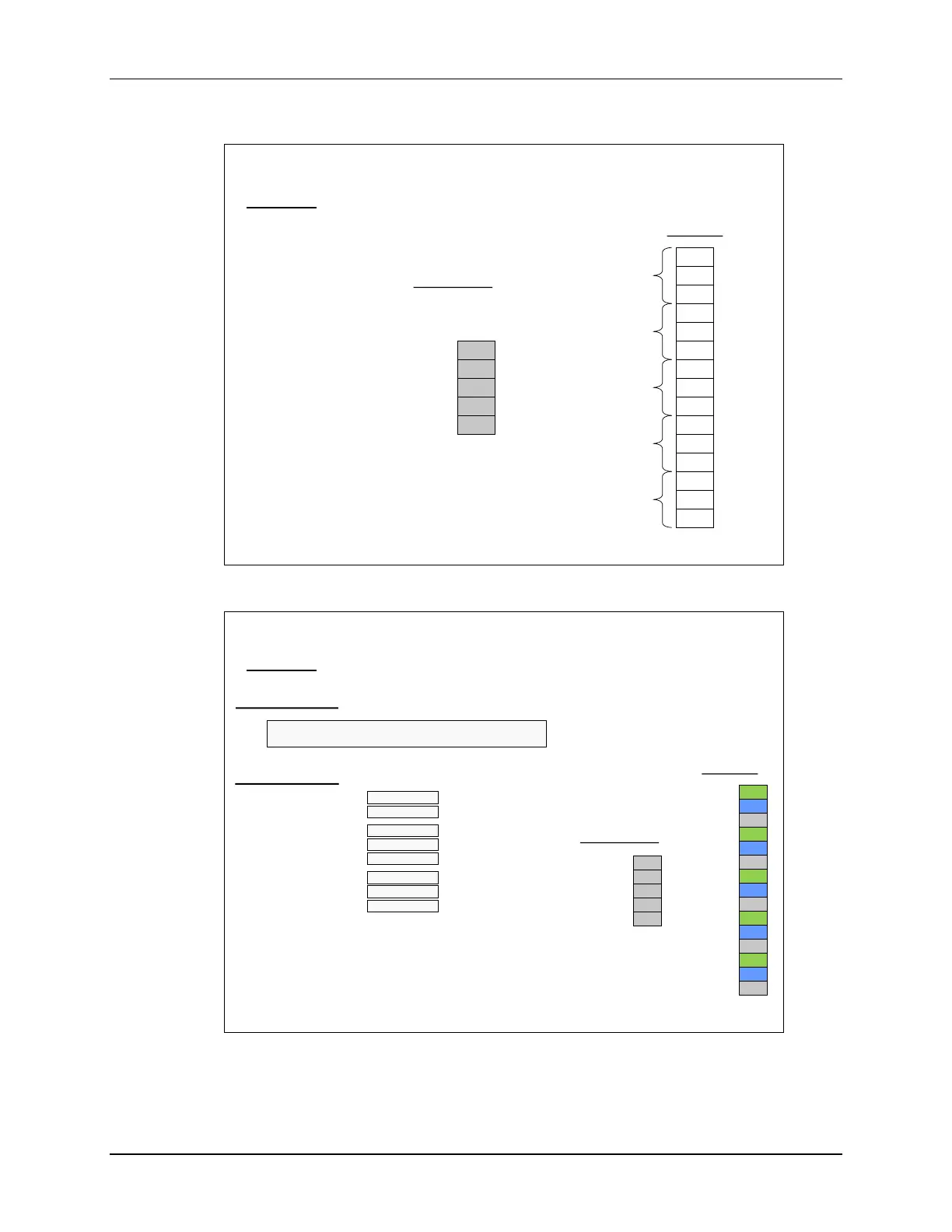

CH4

CH3

CH2

CH1

CH0

0x0B00

0x0B01

0x0B02

ADCA Results

GS3 RAM

0xF000

0xF003

0xF006

0xF009

0xF00C

CH0

CH0

CH0

CH1

CH1

CH1

CH2

CH2

CH2

CH3

CH3

CH3

CH4

CH4

CH4

0xF001

0xF004

0xF007

0xF00A

0xF00D

0xF002

0xF005

0xF008

0xF00B

0xF00E

0x0B03

0x0B04

Objective: Bin 3 samples of 5 ADC channels, then interrupt the CPU

SOC0 – SOC4 configured to CH0 – CH4, respectively,

ADCA configured to re-trigger (continuous conversion)

ADC Registers:

DMA Registers:

0x0000F000

starting address**

** Typically use a relocatable symbol in your code, not a hard value

Loading...

Loading...