Control Law Accelerator (CLA)

9 - 8 TMS320F2837xD Microcontroller Workshop - Control Law Accelerator

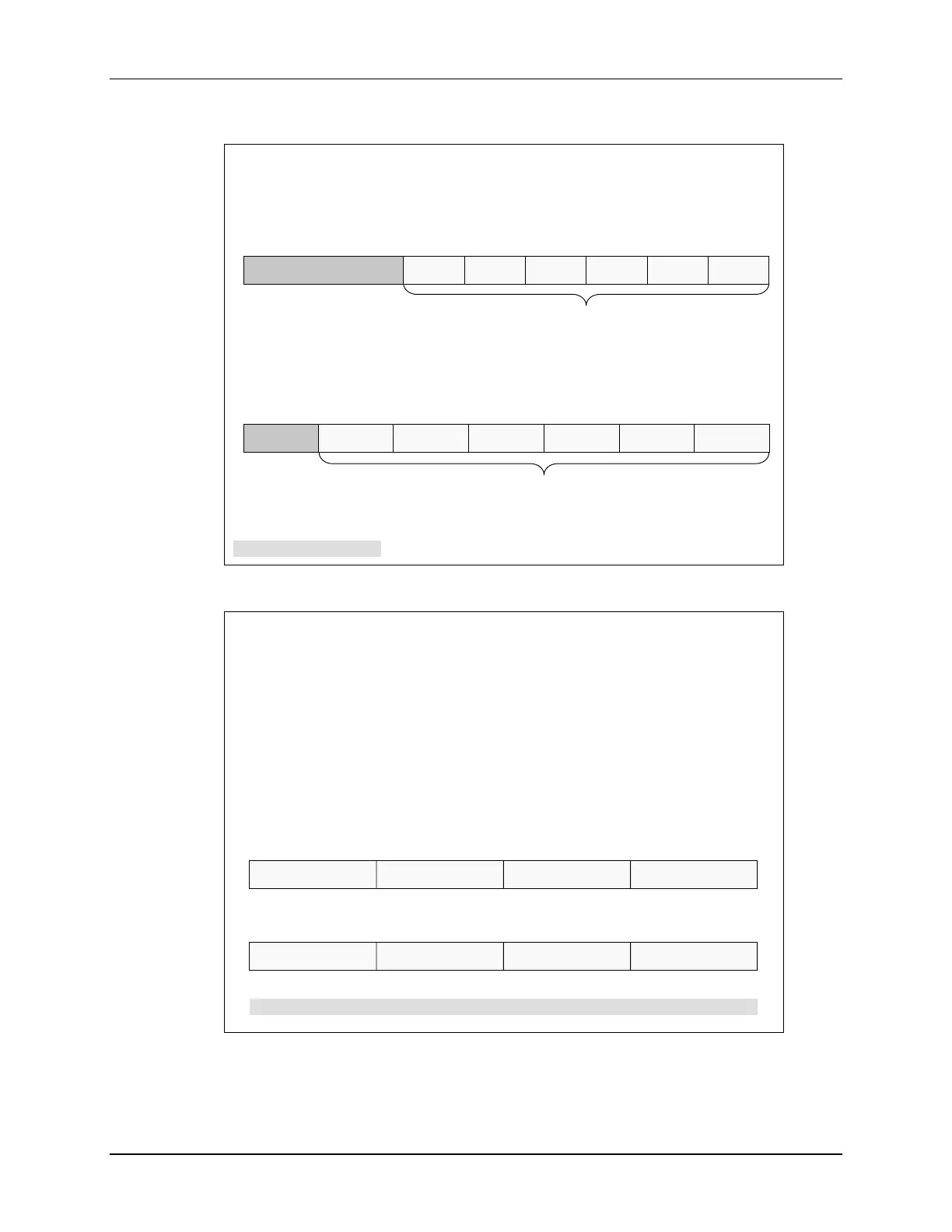

CLA Memory Configuration Registers

Selects LS RAM as program or data CLA memory

0 = CLA data memory

1 = CLA program memory

Master Select for LS RAM

00 = memory is dedicated to CPU

01 = memory is shared between CPU and CLA

1x = reserved

31 - 6

reserved

0

CLAPGM_LS0CLAPGM_LS1CLAPGM_LS2CLAPGM_LS3CLAPGM_LS4CLAPGM_LS5

12345

MemCfgRegs.LSxCLAPGM

MSEL_LS0

1 - 0

5 - 4

reserved

MSEL_LS1MSEL_LS2

MSEL_LS3MSEL_LS4

MSEL_LS5

3 - 2

7 - 69 - 8

11 - 1031 - 12

MemCfgRegs.LSxMSEL

Note: register lock protected

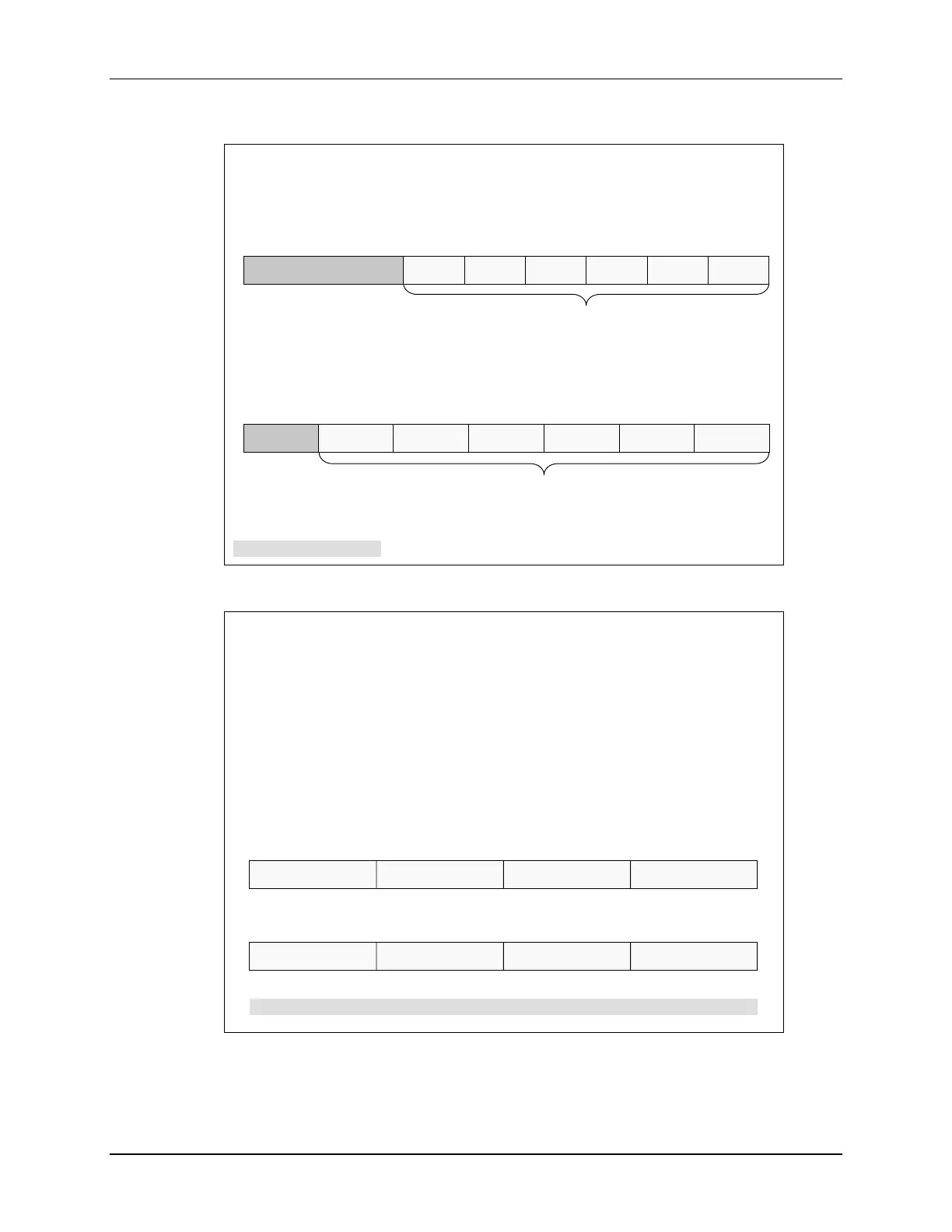

CLA Task Source Selection Registers

Selects the Trigger Source for each Task

Each task can be triggered by up to 256 interrupt sources

Select ‘Software’ if task is unused or software triggered

Default value = Software = 0x00

See “CLA Interrupt Trigger Sources” table on next slide

TASK4

31 - 24 7 - 0

TASK3 TASK2 TASK1

23 - 16 15 - 8

DmaClaSrcSelRegs.CLA1TASKSRCSEL1

TASK8

31 - 24 7 - 0

TASK7 TASK6 TASK5

23 - 16 15 - 8

DmaClaSrcSelRegs.CLA1TASKSRCSEL2

Note: CLA1TASKSRCSELLOCK register can be used to lock above registers (lock bit for each register)

Loading...

Loading...