Oscillator/PLL Clock Module

5 - 4 TMS320F2837xD Microcontroller Workshop - System Initialization

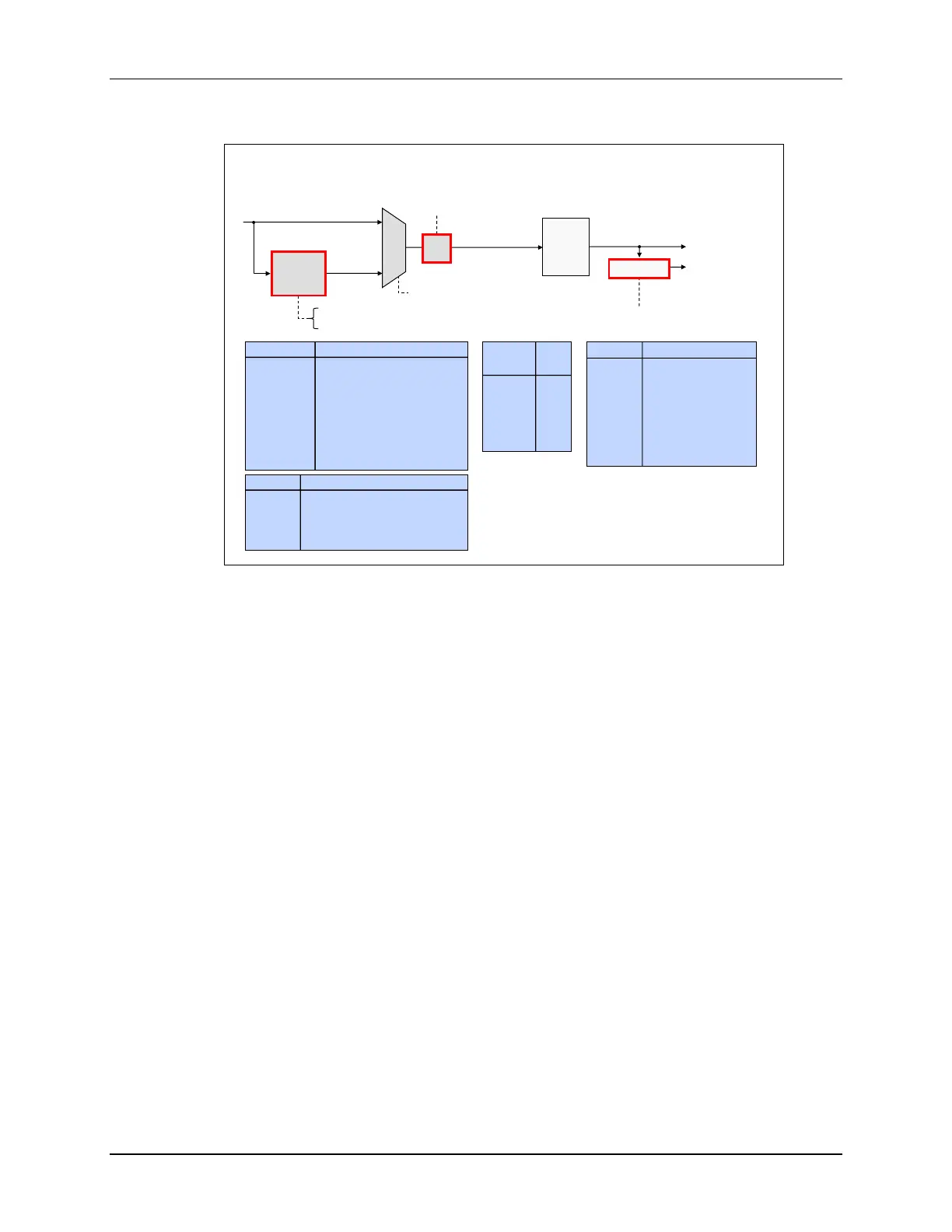

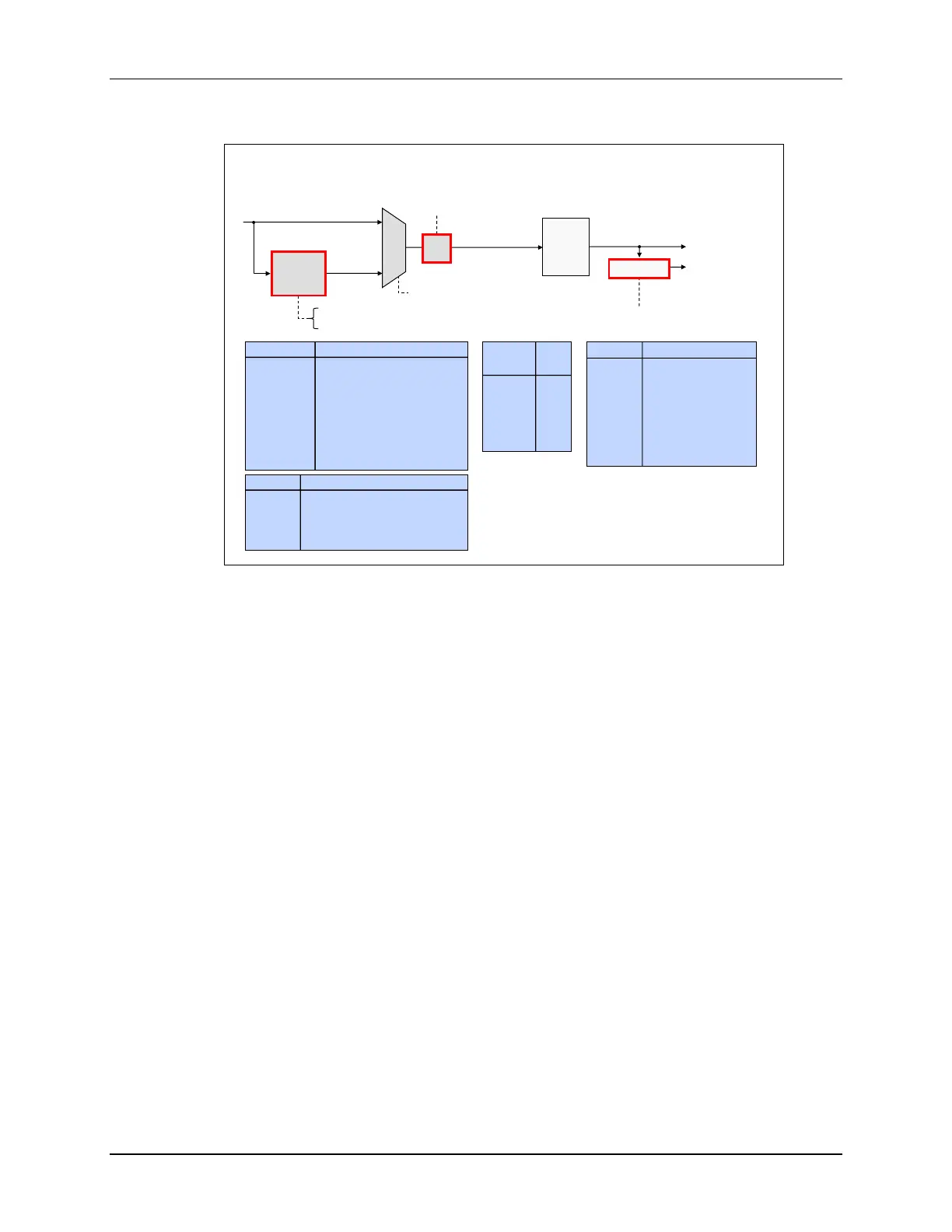

F28x7x PLL and LOSPCP

IMULT CLKIN

0 0 0 0 0 0 0 OSCCLK / n * (PLL bypass)

0 0 0 0 0 0 1 OSCCLK x 1 / n

0 0 0 0 0 1 0 OSCCLK x 2 / n

0 0 0 0 0 1 1 OSCCLK x 3 / n

1 1 1 1 1 0 1 OSCCLK x 125/ n

1 1 1 1 1 1 0 OSCCLK x 126 / n

1 1 1 1 1 1 1 OSCCLK x 127 / n

PLL

PLLCLK

OSCCLK

CPUx

PLLSYSCLK

CPUx.SYSCLK

LOSPCP

(PLL bypass)

CPUx.LSPCLK

MUX

1/n

ClkCfgRegs.SYSPLLMULT.bit.IMULT

ClkCfgRegs.SYSCLKDIVSEL.bit.PLLSYSCLKDIV

ClkCfgRegs.LOSPCP.bit.LSPCLK

LSPCLK Peripheral Clk Freq

0 0 0 CPUx.SYSCLK / 1

0 0 1 CPUx.SYSCLK / 2

0 1 0 CPUx.SYSCLK / 4 *

0 1 1 CPUx.SYSCLK / 6

1 0 0 CPUx.SYSCLK / 8

1 0 1 CPUx.SYSCLK / 10

1 1 0 CPUx.SYSCLK / 12

1 1 1 CPUx.SYSCLK / 14

LSBs in reg. – others reserved

* default

SYSPLL

DIVSEL n

111111 /126

000010 /4 *

000001 /2

000000 /1

• • •

• • •

FMULT CLKIN

0 0 Fractional x 0 *

0 1 Fractional x 0.25

1 0 Fractional x 0.5

1 1 Fractional x 0.75

• • •

• • •

ClkCfgRegs.SYSPLLMULT.bit.FMULT

0*

1

ClkCfgRegs.SYSPLLCTL1.bit.PLLCLKEN

The clock sources can be multiplied using the PLL and divided down to produce the desired clock

frequencies for a specific application. By default, the CPU1 subsystem owns the PLL clock

configuration, however a clock control semaphore is available for the CPU2 subsystem to access

the clock configuration registers.

A clock source can be fed directly into the core or multiplied using the PLL. The PLL gives us the

capability to use the internal 10 MHz oscillator and run the device at the full clock frequency. If

the input clock is removed after the PLL is locked, the input clock failed detect circuitry will issue a

limp mode clock of 1 to 4 MHz. Additionally, an internal device reset will be issued. The low-

speed peripheral clock prescaler is used to clock some of the communication peripherals.

The PLL has a 7-bit integer and 2-bit fractional ratio control to select different CPU clock rates.

The C28x CPU provides a SYSCLK clock signal. This signal is prescaled to provide a clock

source for some of the on-chip communication peripherals through the low-speed peripheral clock

prescaler. Other peripherals are clocked by SYSCLK and use their own clock prescalers for

operation.

Loading...

Loading...