A Instruction Coding

A – 4

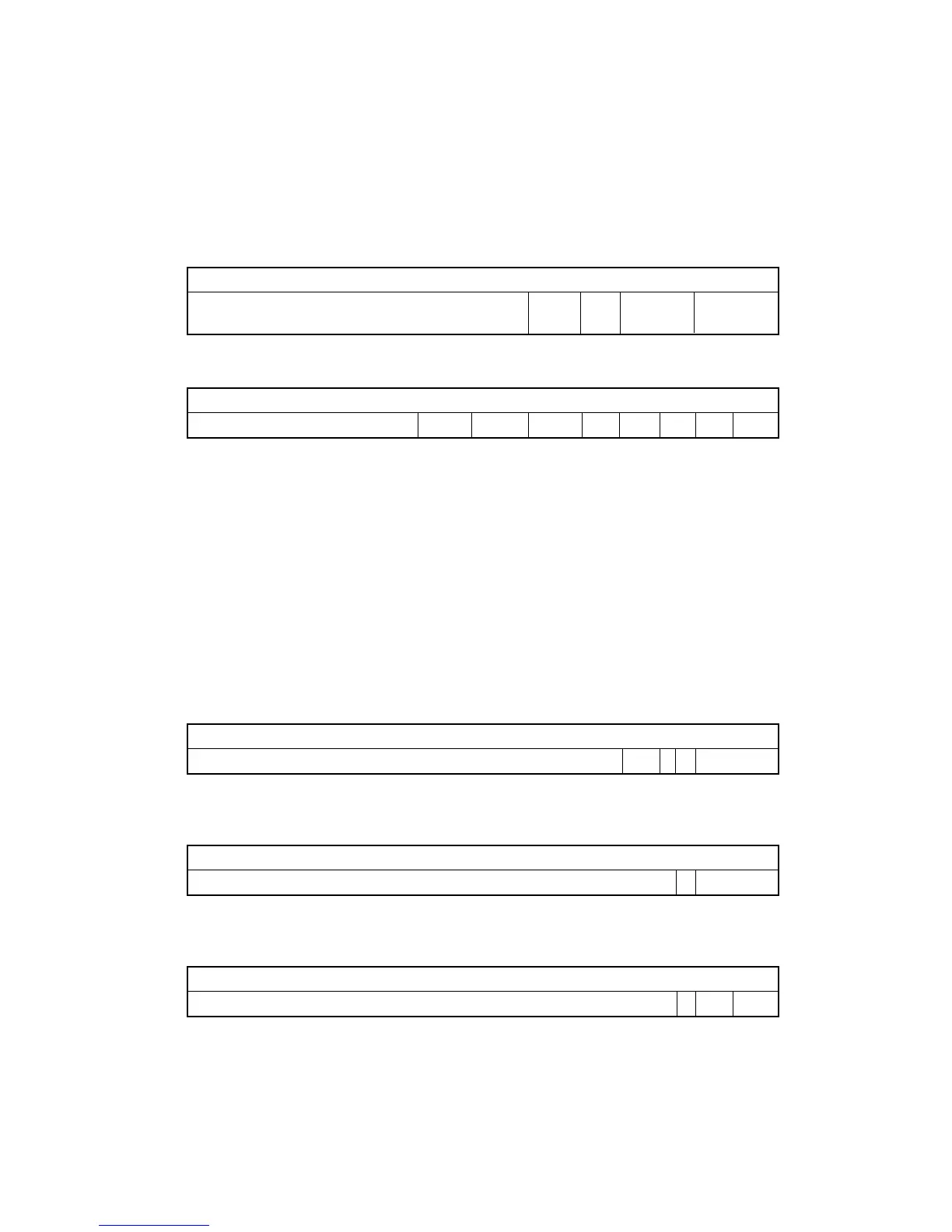

Type 17: Internal Data Move

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 0 1 1 0 1 0 0 0 0 DST SRC Dest Source

RGP RGP REG REG

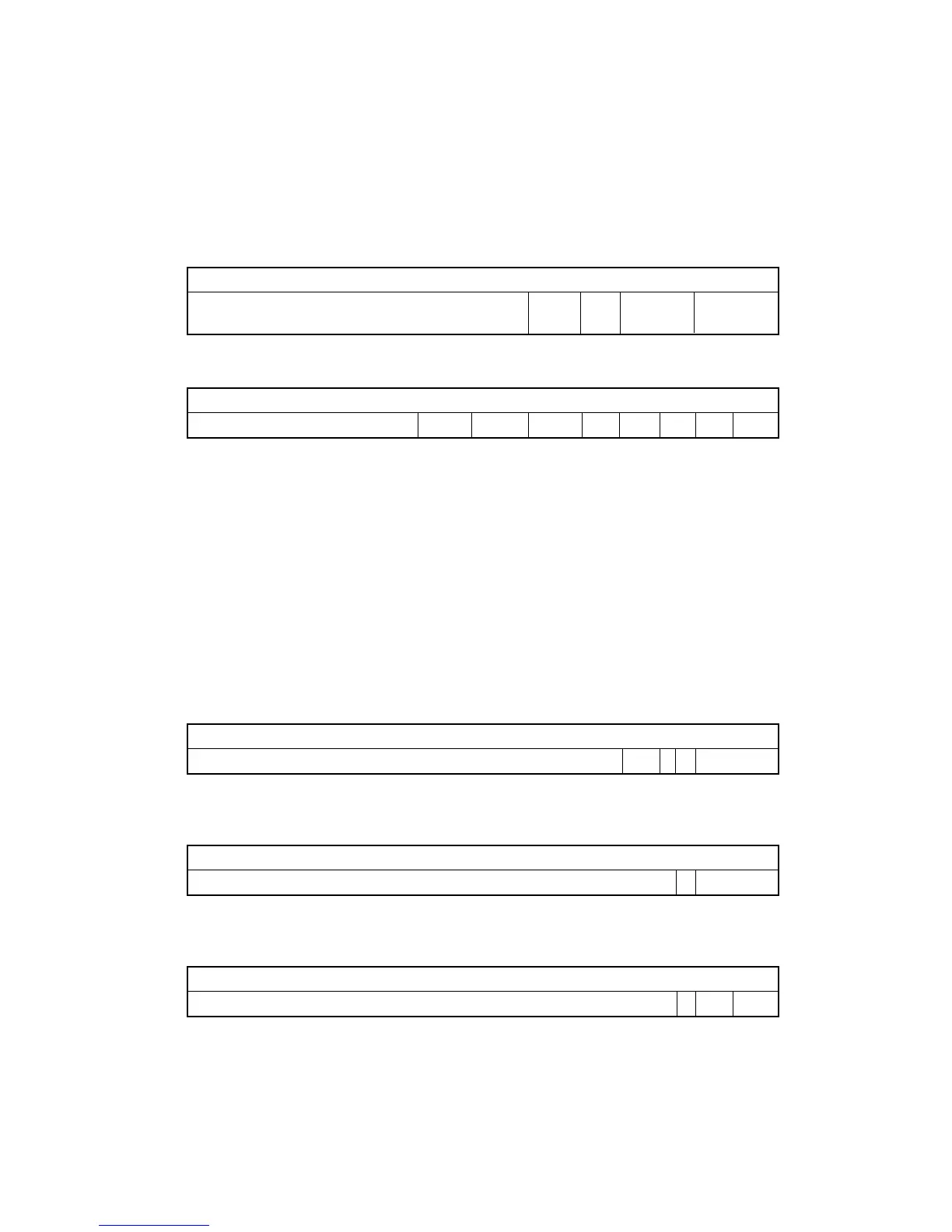

Type 18: Mode Control

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 0 1 1 0 0 TI MM AS OL BR SR GM 0 0

Mode Control codes: SR: Secondary register bank

BR: Bit-reverse mode

OL: ALU overflow latch mode

AS: AR register saturate mode

MM: Alternate Multiplier placement mode

GM: GO Mode; enable means execute internal code if possible

TI: Timer enable

11 = Enable Mode

10 = Disable Mode

0 1 = no change

0 0 = no change

Type 19: Conditional Jump (Indirect Address)

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 0 1 0 1 1 0 0 0 0 0 0 0 0 I 0 S COND

Type 20: Conditional Return

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 T COND

Type 21: Modify Address Register

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 G I M

Loading...

Loading...