60/(set cycle time) comes to an integer. In all other cases the counter values are

transmitted at time intervals determined by a free running internal clock.

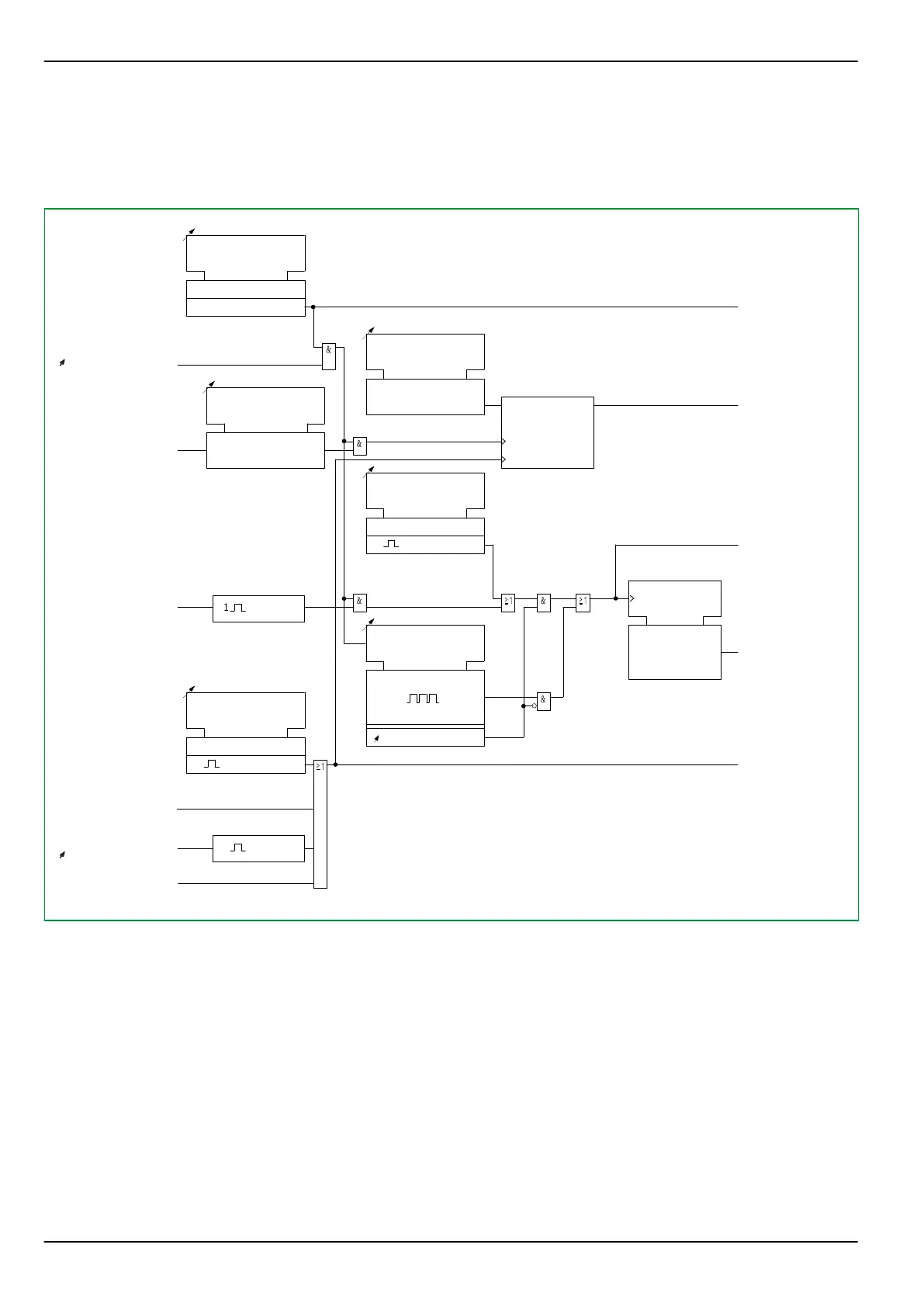

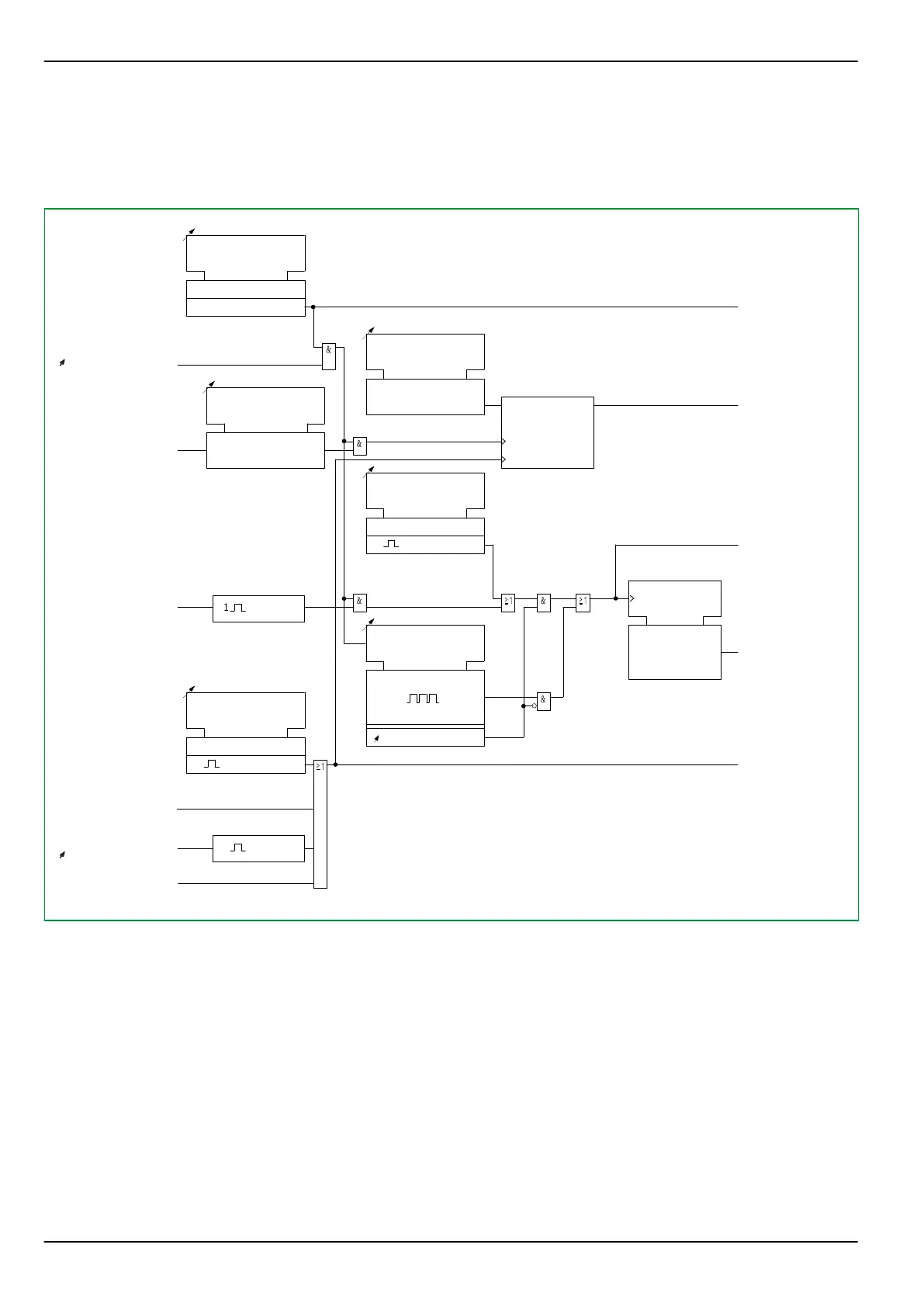

3.36.5 Counter Values Reset

19Z82ANA

1: execute

MAIN:

General reset EXT

[ 005 255 ]

COUNT:

Reset

[ 217 005 ]

MAIN:

General reset USER

[ 003 002 ]

COUNT:

Reset EXT

[ 217 004 ]

0

1

0: don't execute

1: execute

COUNT:

Reset USER

[ 217 003 ]

COUNT:

Transmit counts EXT

[ 217 009 ]

COUNT:

Set counter 1 EXT

[ 217 130 ]

1: Yes (= on)

MAIN:

Device on-line

[ 003 030 ]

Debouncing

0

1

0: No

1: Yes

COUNT:

General enable USER

[ 217 000 ]

COUNT:

Count 1

[ 217 100 ]

COUNT:

Transmit counts USER

[ 217 008 ]

m

CT=m

+

R

COUNT:

Cycle t.count transm

[ 217 007 ]

C

G

= 0 min

C

COMM1:

Count 1

[ --- --- ]

COUNT:

Count 1

[ 217 100 ]

COUNT:

Transmit counts

[ 217 010 ]

COUNT:

Enabled

[ 217 001 ]

0

1

0: don't execute

1: execute

1

COUNT:

Debounce t. count. 1

[ 217 160 ]

Fig. 3-184: Binary Count. (This diagram shows counter 1 as an example. The displayed logic is also valid for

counters 2 to 4, where COUNT: Set counter 1 EXT and COUNT: Count 1 have to be replaced by the

respective parameters.

The counter values may be reset – all at once – by setting parameter

COUNT: Reset USER or via an appropriately configured binary signal input as

well as by the general reset action.

P634

3 Operation

3-228 P634/EN M/R-42-A // P634‑311‑653

Loading...

Loading...