Video Controller

MOTOROLA MPC823e REFERENCE MANUAL 19-25

VIDEO CONTROLLER

19

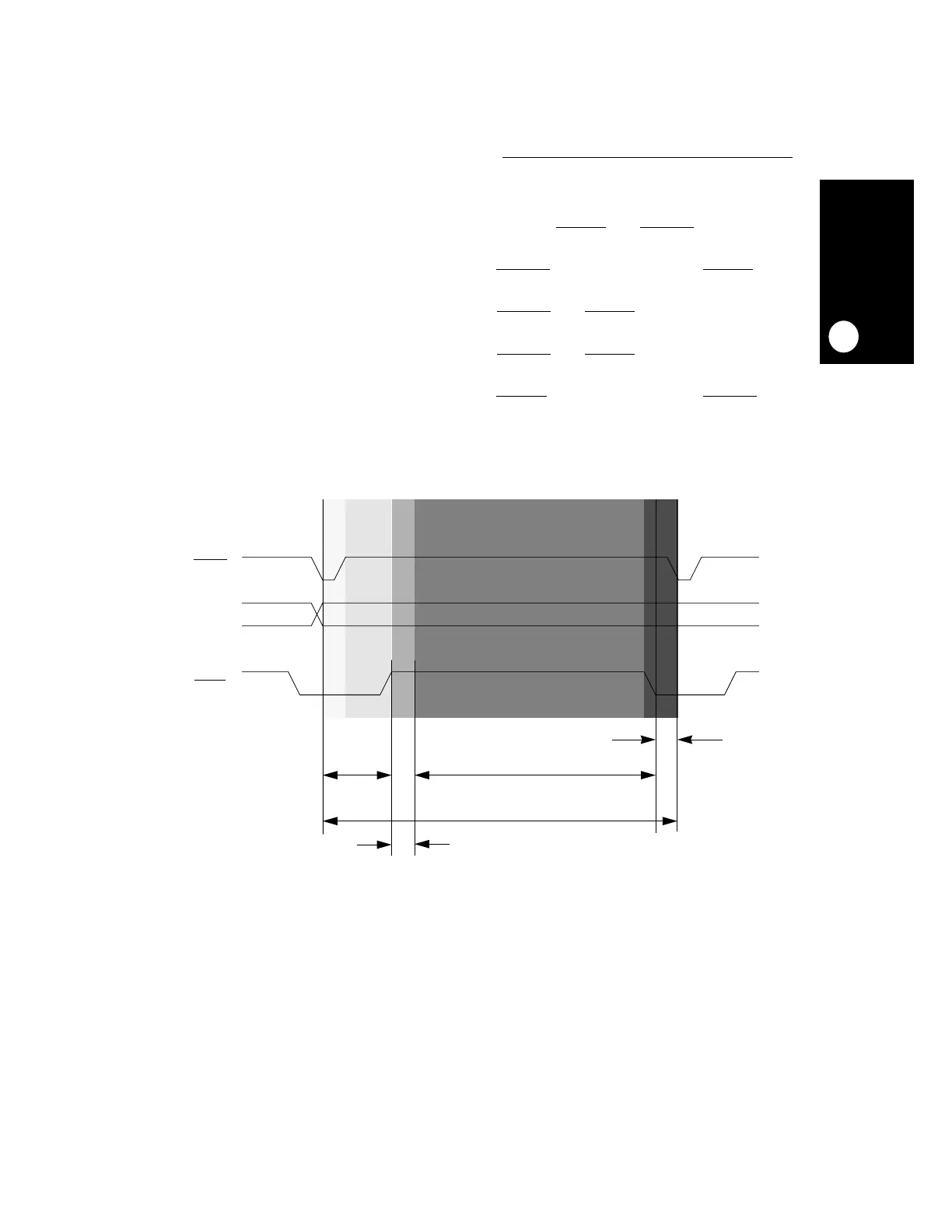

Figure 19-8 illustrates the horizontal timing of a single horizontal line that is represented by

five RAM entries:

• A defines the section of the line where the both the BLANK

and HSYNC signals are

asserted.

• B defines the section of the line where the HSYNC signal is negated and BLANK is

asserted.

• C defines the section of the line where the HSYNC and BLANK signals are negated

while the driven data is background.

• D defines the section of the line where the HSYNC and BLANK signals are negated

while the driven data is the image data.

• E defines the section of the line where the BLANK signal is asserted and HSYNC is

negated.

Figure 19-8. PAL Horizontal Timing

128 PIXELS

(256 CLOCKS)

720 PIXELS

(1440 CLOCKS)

864 PIXELS

(1728 CLOCKS)

LINE 3

LINE 4

HSYNC

FIELD

BLANK

AB D E

C

4 PIXELS

(8 CLOCKS)

12 PIXELS

(24 CLOCKS)

Loading...

Loading...