System Interface Unit

12-8

MPC823e REFERENCE MANUAL

MOTOROLA

SYSTEM INTERFACE UNIT

12

Bits 16–31—Reserved

These bits are reserved and must be set to 0.

12.3.3.2 SIU INTERRUPT MASK REGISTER.

The 32-bit read/write SIU interrupt mask

(SIMASK) register contains bits that individually correspond to the interrupt request bits in

the SIPEND register. When a bit is set, it enables the generation of an interrupt request to

the core. SIMASK is updated by the software and cleared at reset. It is the responsibility of

the software to determine which of the interrupt sources are enabled at a given time.

IRMx—Interrupt Request Mask 0–7

These bits determine whether an IRQx

interrupt service request from an external source is

to be automatically generated to the core. Independent of the IRMx setting, the system

interface unit will automatically set the corresponding IRQx bit in the SIPEND register. See

Figure 12-2 for more information.

0 = Disable automatic generation of an interrupt request to the CPU. You can monitor

the corresponding IRQx bit in the SIPEND register to implement interrupt polling.

1 = Enable automatic generation of an interrupt service request to the CPU, which may

then vector to an interrupt service routine. The EDx bits in the SIEL register

determine if the corresponding IRQx

interrupt is falling edge-triggered or low logical

level triggered. The WMx field in the SIEL register determines if the corresponding

IRQx

interrupt will cause the MPC823e to exit low-power mode.

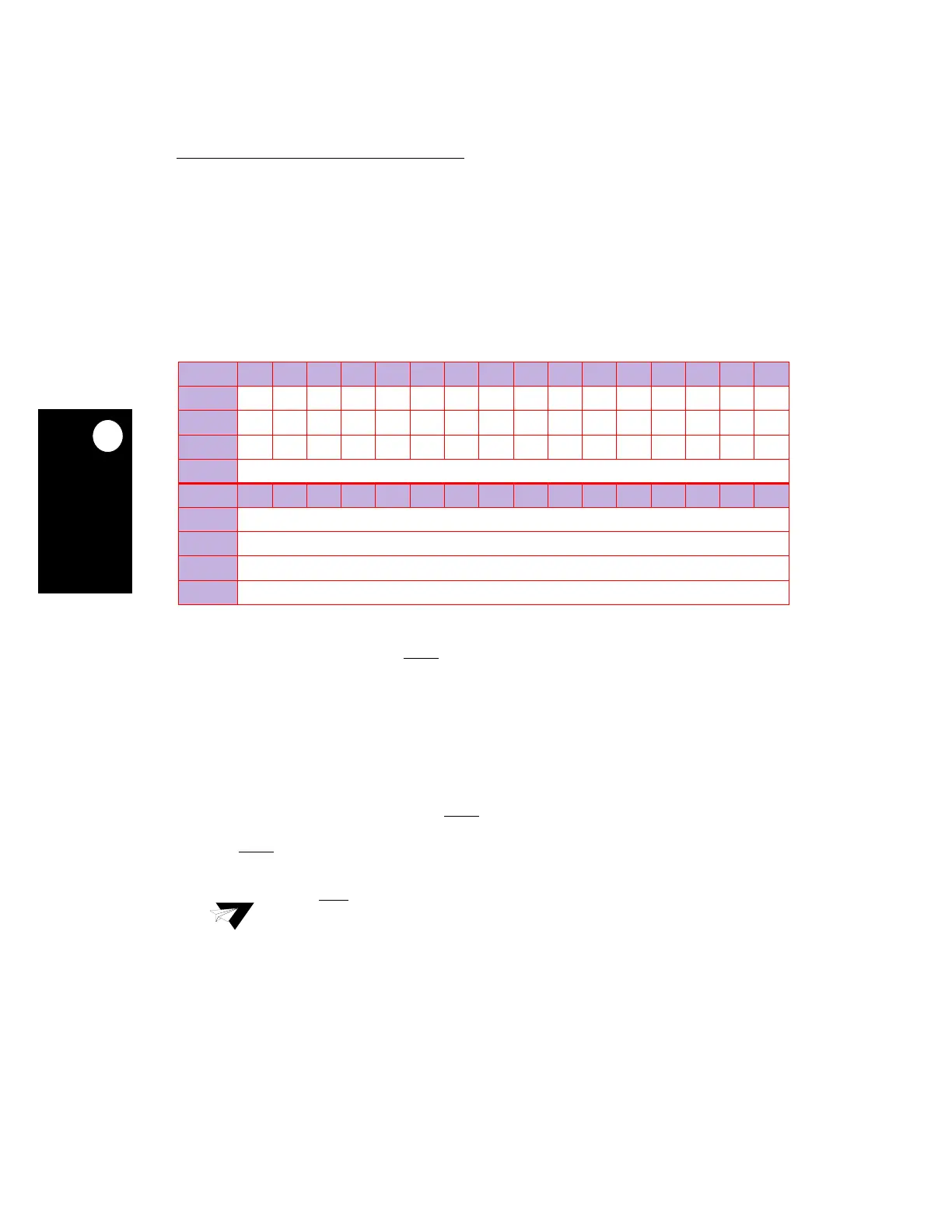

SIMASK

BIT

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

FIELD

IRM0 LVM0 IRM1 LVM1 IRM2 LVM2 IRM3 LVM3 IRM4 LVM4 IRM5 LVM5 IRM6 LVM6 IRM7 LVM7

RESET

0000000000000000

R/W

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

ADDR

(IMMR & 0xFFFF0000) + 0x014

BIT

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

FIELD

RESERVED

RESET

0

R/W

R/W

ADDR

(IMMR & 0xFFFF0000) + 0x016

Note:

IRQ0

will generate a non-maskable interrupt even if its corresponding IRM0 bit

is not set.

Loading...

Loading...